### LOONGSON

# ■ 龙芯 1F 处理器用户手册 ■

1.3版

2010年11月

北京龙芯中科技术服务中心有限公司

# 修订历史

| 日期         | 编者   | 版本  | 变化                   |

|------------|------|-----|----------------------|

| 2010-6-7   | 研发中心 | 1.0 | 1F 处理器初稿完成           |

| 2010-11-13 | 研发中心 | 1.1 | 增加了芯片引脚排布,DDR 控制器信息等 |

| 2010-11-15 | 研发中心 | 1.2 | 修改并进行标准排版            |

| 2010-11-15 | 研发中心 | 1.3 | 修订了第五章 DDR 的部分错误     |

|            |      |     |                      |

|            |      |     |                      |

|            |      |     |                      |

### 目 录

| 1 | 概述   | <u>.</u> |                  | 1   |

|---|------|----------|------------------|-----|

|   | 1.1  | 体系结构     | 勾框图              | 2   |

|   | 1.2  | 芯片主要     | 导功能              | 2   |

|   |      | 1.2.1    | GS232 CPU        | 2   |

|   |      | 1.2.2    | AMBA错误! 未定义书签    | -   |

|   |      | 1.2.3    | DDR2             | 3   |

|   |      | 1.2.4    | PCI              | 4   |

|   |      | 1.2.5    | 2D GPU           | 4   |

|   |      | 1.2.6    | LCD Controller   | 4   |

|   |      | 1.2.7    | SATA             | 5   |

|   |      | 1.2.8    | USB2.0           | 5   |

|   |      | 1.2.9    | AC97             | 5   |

|   |      | 1.2.10   | GMAC             | 5   |

|   |      | 1.2.11   | LPC              | 5   |

|   |      | 1.2.12   | SPI              | 6   |

|   |      | 1.2.13   | UART             | 6   |

|   |      | 1.2.14   | l <sup>2</sup> C | 6   |

|   |      | 1.2.15   | PWM              | 6   |

|   |      | 1.2.16   | NAND             | 7   |

|   |      | 1.2.17   | CAN              | 7   |

|   |      | 1.2.18   | RTC              | 7   |

|   |      | 1.2.19   | GPIO             | 7   |

|   |      | 1.2.20   | INT controller   | 7   |

|   |      | 1.2.21   | PS2              | 7   |

|   |      | 1.2.22   | Watchdog         | 7   |

|   |      | 1.2.23   | ACPI             | 8   |

|   |      | 1.2.24   | 其它               | 8   |

| 2 | 芯片   | 引脚定义     | <u> </u>         | 9   |

|   | 2.1  | 1F引脚分    | }布图              | 9   |

|   | 2.2  | 系统相关     | <b>长引脚定义(8)</b>  | .20 |

|   | 2.3  | DC引脚     | 定义(28)           | .20 |

|   | 2.4  | PLL引脚    | 『定义(20)          | .21 |

|   | 2.5  | VR引脚     | 定义(6)            | .21 |

|   | 2.6  | DDR2 弓   | 脚定义(75)          | .21 |

|   | 2.7  | USB引肽    | 甲定义(10)          | .23 |

|   | 2.8  | JTAG引    | 脚定义(6)           | .24 |

|   | 2.9  | GMAC0    | 引脚定义(15)         | .24 |

|   | 2.10 | GMAC1    | 引脚定义(3)          | .24 |

|   | 2.11 | AC97 引   | 脚定义(5)           | .24 |

|   | 2.12 | SPI引脚    | 定义(8)            | .25 |

|   | 2.13 | UART引    | 脚定义(16)          | .25 |

| 2 | 2.14 | I2C引脚舞  | 定义(2)                            | 25  |

|---|------|---------|----------------------------------|-----|

| 2 | 2.15 | CAN引肽   | 即定义(4)                           | 26  |

| 2 | 2.16 | NAND引   | 脚定义(8)                           | 26  |

| 2 | 2.17 | PWM引加   | 却定义(4)                           | 26  |

| 2 | 2.18 | LPC引脚   | 定义(6)                            | 26  |

| 2 | 2.19 | PCI引脚類  | 定义(55)                           | 26  |

| 2 | 2.20 | SATA引用  | 脚定义(11)                          | 28  |

| 2 | 2.21 | ACPI引腿  | 即定义(15)                          | 28  |

| 2 | 2.22 | PS2 引脚  | 定义(4)                            | 29  |

| 2 | 2.23 | VGA引肽   | 『定义(10)                          | 21  |

| 2 | 2.24 | 电源/地引   | ·  脚(4)                          | 29  |

| 3 | 地址   | :空间分配   |                                  | 31  |

| 3 | 3.1  | 一级AXI   | 交叉开关上模块的地址空间                     | 31  |

| 3 | 3.2  | AXI-MU  | X下各模块的地址空间                       | 31  |

| 3 | 3.3  | APB各模   | 5块的地址空间分配                        | 32  |

| 4 | CPL  | J       |                                  | 33  |

| 4 | l. 1 |         | 旨令系统结构                           |     |

|   |      | 4. 1. 1 | CPU寄存器                           | 34  |

|   |      | 4. 1. 2 | CPU指令集                           | 35  |

|   |      | 4. 1. 3 | CP0 指令集                          | 39  |

|   |      | 4. 1. 4 | 存储空间                             | 40  |

|   |      | 4. 1. 5 | 例外处理                             | 41  |

|   |      | 4. 1. 6 | CP0 寄存器                          | 43  |

|   | 1.2  | CP0 指令  | `                                | 63  |

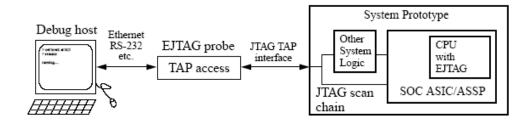

| 4 | 1.3  | EJTAG设记 | 计                                | 64  |

|   |      | 4. 3. 1 | EJTAG介绍                          |     |

|   |      | 4. 3. 2 | 调试控制寄存器 (Debug Control Register) |     |

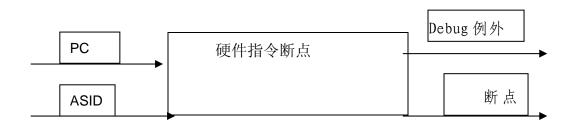

|   |      | 4. 3. 3 | 硬件断点                             |     |

|   |      |         | BJTAG相关的处理器核扩展                   |     |

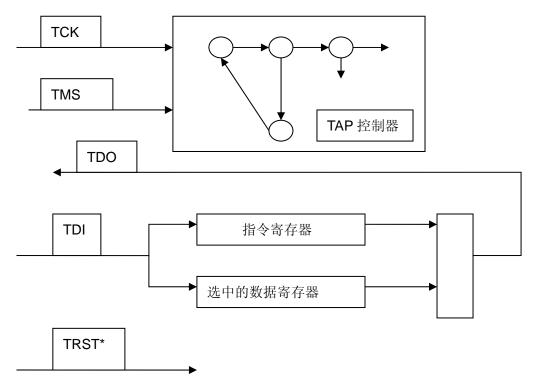

|   |      | 4. 3. 5 | TAP接口                            | 76  |

| 5 |      |         |                                  |     |

|   |      |         | DRAM控制器特性                        |     |

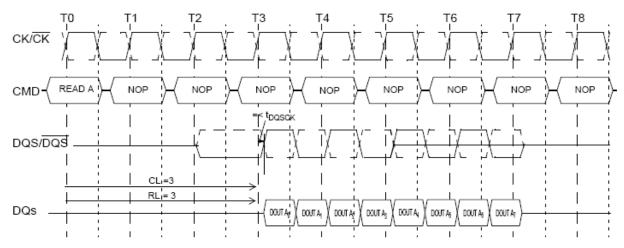

|   |      |         | DRAM 读协议                         |     |

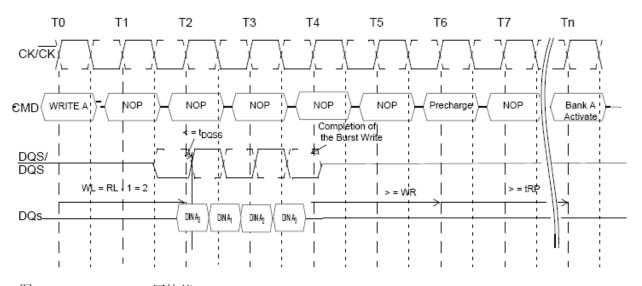

|   |      |         | DRAM写协议                          |     |

|   |      |         | DRAM 参数设置顺序                      |     |

|   | 5.5  |         | DRAM 采样模式配置                      |     |

|   |      |         |                                  |     |

|   | 5.1  |         | <u> </u>                         |     |

|   | 5.2  |         | i述                               |     |

|   |      |         | le- res                          |     |

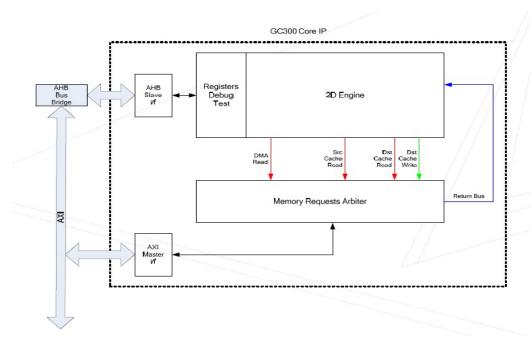

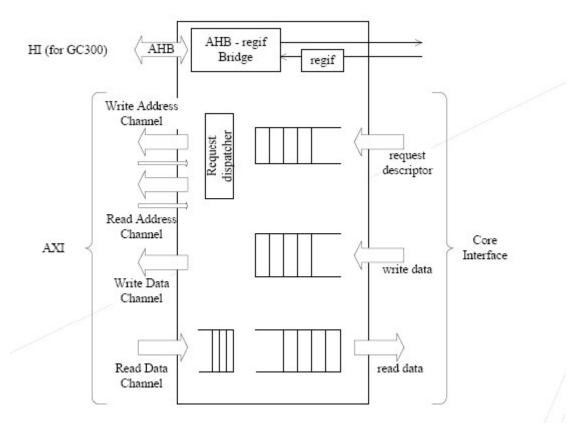

|   | 7.1  | _       | CK框图                             |     |

|   | 7.2  |         | J                                |     |

| 7 | 7.3  |         | 月擎                               |     |

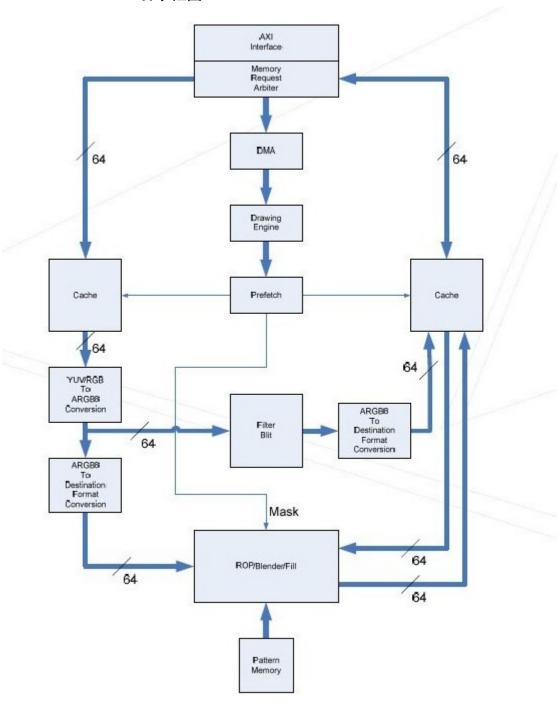

|   |      | 7.3.1   | 2D GPU引擎框图                       | 105 |

|     |      | 7.3.2  | 2D GPU引擎支持的硬件图元操作                     |      | 105    |

|-----|------|--------|---------------------------------------|------|--------|

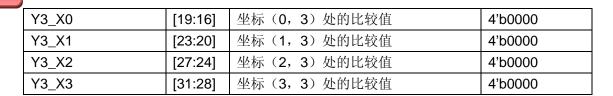

|     | 7.4  | GPU内音  | 『寄存器列表                                |      | 108    |

| 8   | LCD  | )      |                                       |      | 113    |

|     | 8.1  | 特性     |                                       |      | 113    |

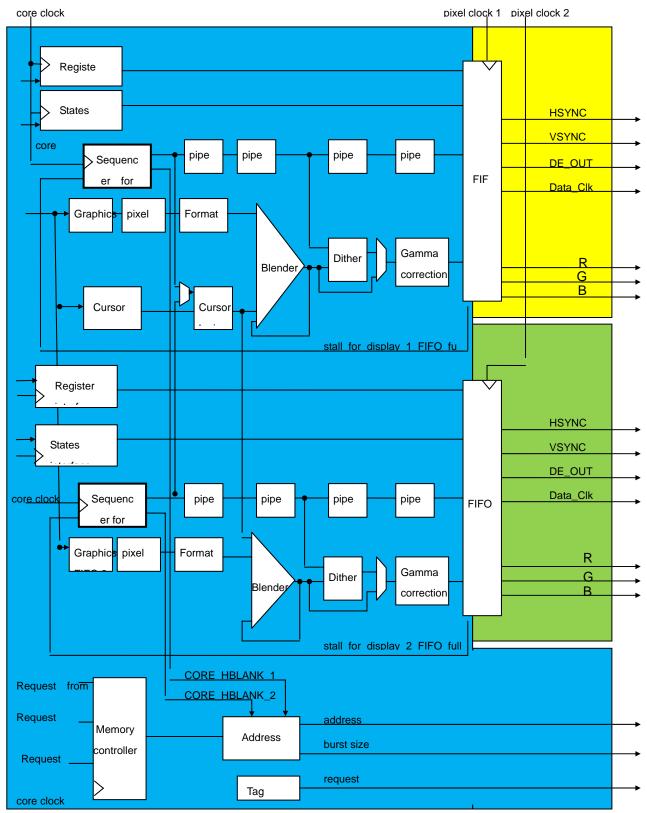

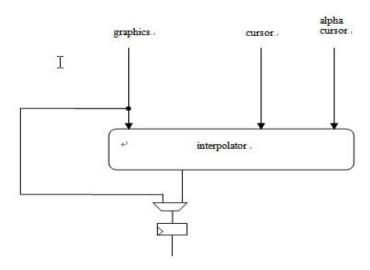

|     | 8.2  | 模块示意   | [图                                    |      | 113    |

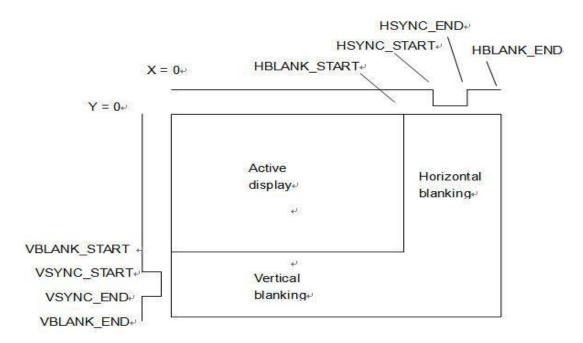

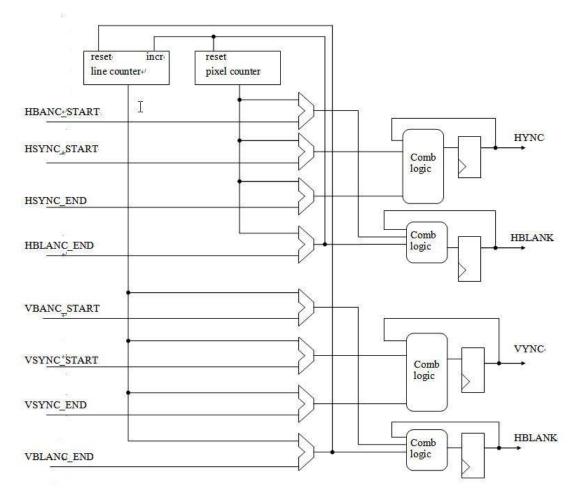

|     | 8.3  | VTG 定  | ·<br>字器                               |      | 115    |

|     | 8.4  | 合并模划   | <u>.</u>                              |      | 116    |

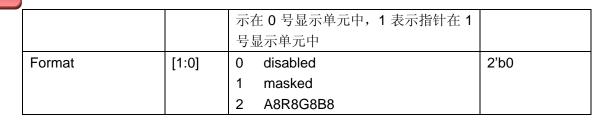

|     | 8.5  | 格式转换   | 1                                     |      | 117    |

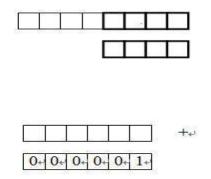

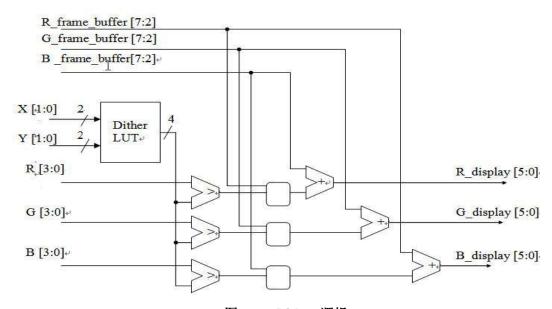

|     | 8.6  | 颜色抖动   | J                                     |      | 117    |

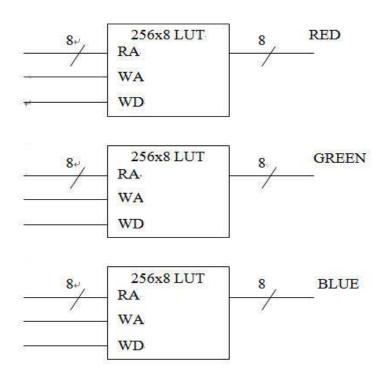

|     | 8.7  | GAMMA  | 周整                                    |      | 118    |

|     | 8.8  | 访存     |                                       |      | 119    |

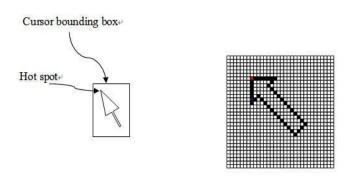

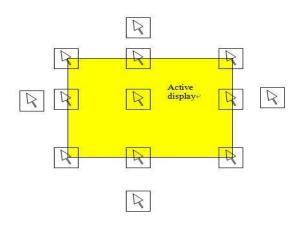

|     | 8.9  | 指针     |                                       |      | 119    |

|     | 8.10 | 访存地址   | 上的生成                                  |      | 120    |

|     |      | 8.10.1 | Bursts                                |      | 121    |

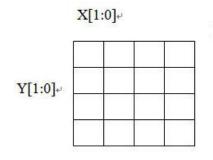

|     |      | 8.10.2 | 数据格式                                  |      | 121    |

|     |      | 8.10.3 | 内存组织                                  |      | 121    |

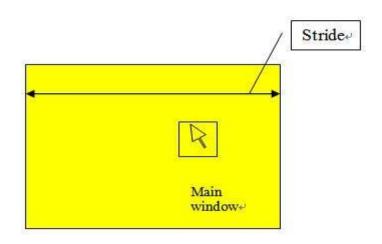

|     |      | 8.10.4 | 跨度                                    |      | 121    |

|     | 8.11 | 核心时钟   | 中域的定序器                                |      | 122    |

|     | 8.12 | 输入数据   | FIFOs                                 |      | 122    |

|     | 8.13 | 关于VBI  | _ANK的同步                               |      | 122    |

|     | 8.14 | AXI接口  |                                       |      | 122    |

|     | 8.15 |        |                                       |      |        |

| 9   | GMA  | AC0    |                                       | .错误! | 未定义书签。 |

|     | 9.1  | DMA寄   | 字器                                    | .错误! | 未定义书签。 |

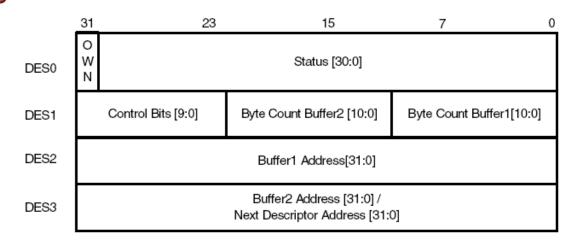

|     | 9.2  |        | ·<br>空制器描述符                           |      |        |

|     | 9.3  |        | <b>本符</b>                             |      |        |

|     |      | 9.3.1  | <br>DMA描述符的基本格式                       |      |        |

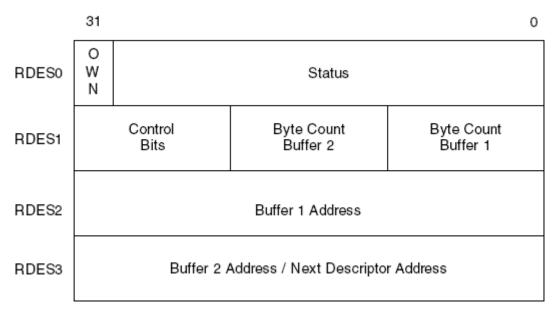

|     |      | 9.3.2  | DMA接收描述符                              |      |        |

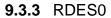

|     |      | 9.3.3  | RDES0                                 |      |        |

| 10  | 0    | GMAC1  |                                       |      |        |

|     | 10.1 |        | 外部信号复用和配置                             |      |        |

|     | 10.2 |        | 字器                                    |      |        |

|     | 10.3 |        | ·<br>E制器描述符                           |      |        |

|     | 10.4 |        | ▲符                                    |      |        |

|     |      |        |                                       |      |        |

|     |      |        | DMA接收描述符                              |      |        |

|     |      |        | RDES0                                 |      |        |

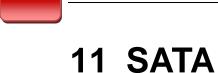

| 11  | 1    |        |                                       |      |        |

| •   | 11.1 |        | ************************************* |      |        |

|     | 11.2 |        | 存器描述                                  |      |        |

| 12  |      |        | 9ST                                   |      |        |

| . 4 | 12.1 |        | <u> </u>                              |      |        |

|     |      |        | ·<br>L控制器寄存器                          |      |        |

|     | 14.4 |        | FHCI相关客存器                             |      |        |

|      | 12.2.2     | Capability寄存器                |       | 167 |

|------|------------|------------------------------|-------|-----|

|      | 12. 2. 3   | Operational寄存器               |       | 168 |

|      | 12.2.4     | EHCI Synopsys-Specific 寄存器   |       | 168 |

|      | 12.2.5     | INSNREG00 寄存器                |       | 168 |

|      | 12.2.6     | INSNREG01 寄存器                |       | 169 |

|      | 12.2.7     | INSNREG02 寄存器                |       | 169 |

|      | 12.2.8     | INSNREG03 寄存器                |       | 169 |

|      | 12.2.9     | INSNRE04 寄存器                 |       | 169 |

|      | 12.2.10    | INSNRE05 寄存器                 |       | 170 |

|      | 12.2.11    | INSNREG06 寄存器                |       | 170 |

|      | 12.2.12    | INSNREG07 寄存器                |       | 170 |

|      | 12.2.13    | INSNREG08 寄存器                |       | 170 |

| 12.3 | OHCI相      | 关寄存器                         |       | 171 |

|      | 12.3.1     | Operational寄存器               |       | 171 |

|      | 12.3.2     | OHCI Synopsys-Specific寄存器    |       | 171 |

|      | 12.3.3     | INSNREG06 寄存器                |       | 172 |

|      | 12.3.4     | INSNREG07 寄存器                |       | 172 |

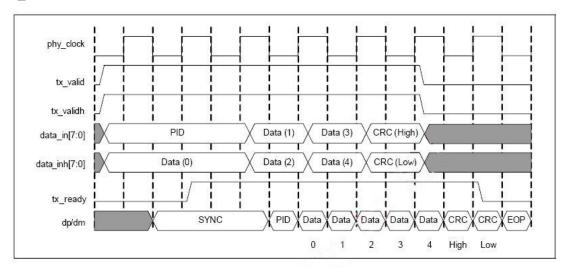

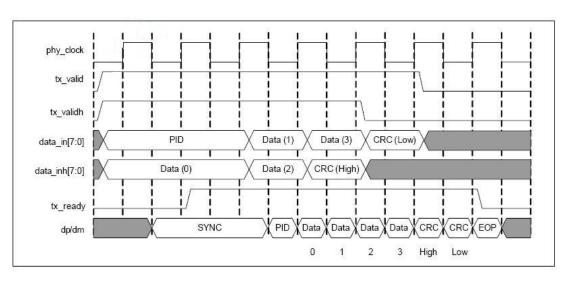

| 12.4 | USB主机      | L控制器时序                       |       | 172 |

|      | 12.4.1     | 数据接收时序                       |       | 172 |

|      | 12.4.2     | 数据传输时序                       |       | 173 |

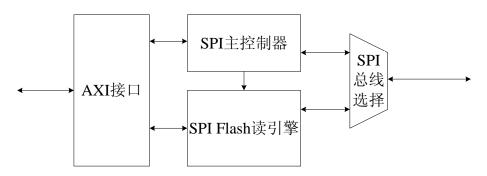

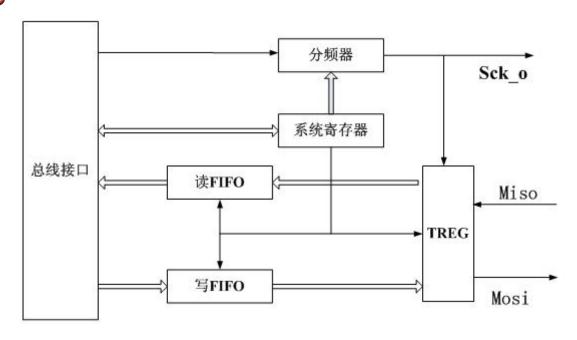

| 13   | SPI0       |                              |       | 175 |

| 13.1 | SPI主控      | 制器结构                         |       | 175 |

| 13.2 | SPI控制      | 器寄存器                         |       | 176 |

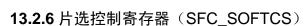

|      | 13.2.1     | 控制寄存器(SPCR)                  |       | 176 |

|      | 13.2.2     | 状态寄存器(SPSR)                  |       | 176 |

|      | 13.2.3     | 数据寄存器(TxFIFO/RxFIFO)         |       |     |

|      | 13.2.4     | 外部寄存器(SPER)                  |       | 177 |

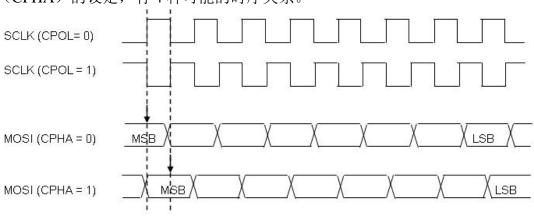

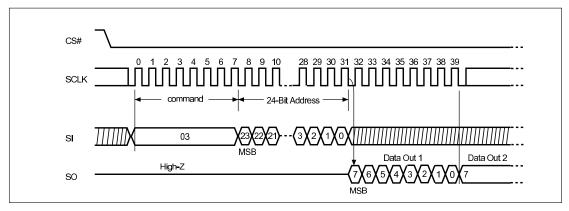

|      | 13.2.5     | 参数控制寄存器(SFC_PARAM)           |       | 177 |

|      | 13.2.6     | 片选控制寄存器(SFC_SOFTCS)          |       |     |

|      | 13.2.7     | 时序控制寄存器(SFC_TIMING)          |       | 178 |

| 14   | SPI1       |                              |       | 182 |

| 14.1 |            | 制器结构                         |       |     |

| 14.2 | SPI控制      | 器寄存器 <b>错</b>                |       |     |

|      | 14.2.1     | 控制寄存器 (SPCR) <b>错</b>        |       |     |

|      | 14.2.2     | 状态寄存器 (SPSR) <b>错</b>        |       |     |

|      | 14.2.3     | 数据寄存器(TxFIFO/RxFIFO)错        |       |     |

|      | 14.2.4     | 外部寄存器(SPER)错                 |       |     |

|      | 14.2.5     | 参数控制寄存器(SFC_PARAM)错          |       |     |

|      | 14.2.6     | 片选控制寄存器(SFC_SOFTCS)错         |       |     |

|      | 14.2.7     | 时序控制寄存器(SFC_TIMING) <b>错</b> |       |     |

| 15   |            | d Interrupt                  |       |     |

| 15.1 |            | ¬断控制器总体描述                    |       |     |

| 15.2 |            | 器寄存器描述                       | ••••• |     |

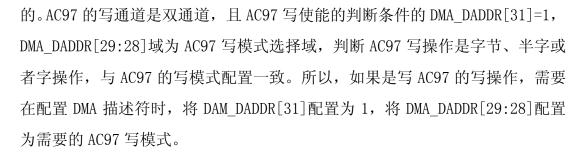

| 16   | $DM\Delta$ |                              |       | 197 |

| 16.1 | DMA控   | 制器结构描述            | 187 |

|------|--------|-------------------|-----|

| 16.2 | DMA控   | 制器与APB设备的交互       | 187 |

| 16.3 | DMA控   | 制器                | 188 |

|      | 16.3.1 | DMA_SADDR         | 188 |

|      | 16.3.2 | DMA_DADDR         | 188 |

|      | 16.3.3 | DMA_LENGTH        | 189 |

|      | 16.3.4 | DMA_STEP_LENGTH   | 189 |

|      | 16.3.5 | DMA_STEP_TIMES    | 189 |

|      | 16.3.6 | DMA_CMD           | 189 |

|      | 16.3.7 | ORDER_ADDR_IN     | 190 |

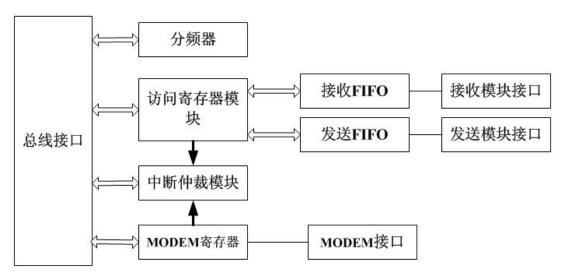

| 17   | UART   |                   | 191 |

| 17.1 | UART挖  | 空制器结构             | 191 |

| 17.2 | UART挖  | 空制器寄存器            | 192 |

|      | 17.2.1 | 数据寄存器(DAT)        | 192 |

|      | 17.2.2 | 中断使能寄存器(IER)      |     |

|      | 17.2.3 | 中断标识寄存器(IIR)      | 193 |

|      | 17.2.4 | FIFO控制寄存器(FCR)    |     |

|      | 17.2.5 | 线路控制寄存器(LCR)      |     |

|      | 17.2.6 | MODEM控制寄存器(MCR)   |     |

|      | 17.2.7 | 线路状态寄存器(LSR)      |     |

|      | 17.2.8 | MODEM状态寄存器 (MSR)  |     |

|      | 17.2.9 | 分频锁存器             |     |

| 18   |        |                   |     |

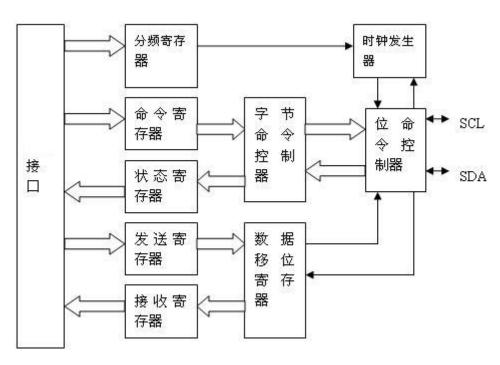

| 18.1 |        | 制器结构              |     |

| 18.2 |        | 式                 |     |

|      | 18.2.1 | 标准模式地址表           |     |

|      | 18.2.2 | 控制寄存器 (CR)        |     |

|      | 18.2.3 | 命令寄存器(CMR)        |     |

|      | -      | 状态寄存器(SR)         |     |

|      | 18.2.5 | 中断寄存器(IR)         |     |

|      | 18.2.6 | 验收代码寄存器(ACR)      |     |

|      | 18.2.7 | 验收屏蔽寄存器(AMR)      |     |

|      | 18.2.8 | 发送缓冲区列表           |     |

|      | 18.2.9 | 接收缓冲区列表           |     |

| 18.3 |        | 式                 |     |

|      | 18.3.1 | 扩展模式地址表           |     |

|      | 18.3.2 | 模式寄存器(MOD)        |     |

|      | 18.3.3 | 命令寄存器(CMR)        |     |

|      | 18.3.4 | 状态寄存器(SR)         |     |

|      | 18.3.5 | 中断寄存器(IR)         |     |

|      | 18.3.6 | 中断使能寄存器(IER)      |     |

|      | 18.3.7 | 仲裁丢失捕捉寄存器(IER)    |     |

|      | 18.3.8 | 错误警报限制寄存器(EMLR)   |     |

|      | 1839   | RX错误计数寄存器 (RXFRR) | 205 |

|      | 18.3.10            | TX错误计数寄存器(TXERR)    | 206      |

|------|--------------------|---------------------|----------|

|      | 18.3.11            | 验收滤波器               | 206      |

|      | 18.3.12            | RX信息计数寄存器(RMCR)     | 206      |

| 18.4 | 公共寄存               | 7器                  | 206      |

|      | 18.4.1             | 总线定时寄存器 0 (BTR0)    | 206      |

|      | 18.4.2             | 总线定时寄存器 1 (BTR1)    | 206      |

|      | 18.4.3             | 输出控制寄存器(OCR)        | 207      |

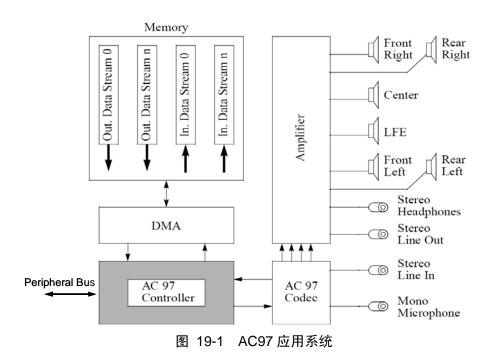

| 19   | AC97               |                     | 208      |

| 19.1 | AC97 结             | 构描述                 | 208      |

| 19.2 | AC97 控             | 制器寄存器               | 208      |

|      | 19.2.1             | CSR寄存器              | 209      |

|      | 19.2.2             | OCC寄存器              | 209      |

|      | 19.2.3             | ICC寄存器              | 210      |

|      | 19.2.4             | (输入输出)通道寄存器配置       | 210      |

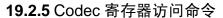

|      | 19.2.5             | Codec寄存器访问命令        | 211      |

|      | 19.2.6             | 中断状态寄存器/中断掩膜寄存器     | 211      |

|      | 19.2.7             | 中断状态/清除寄存器          | 211      |

|      | 19.2.8             | OC中断清除寄存器           | 212      |

|      | 19.2.9             | IC中断清除寄存器           | 212      |

|      | 19.2.10            | CODEC WRITE 中断清除寄存器 | 212      |

|      | 19.2.11            | CODEC READ 中断清除寄存器  | 212      |

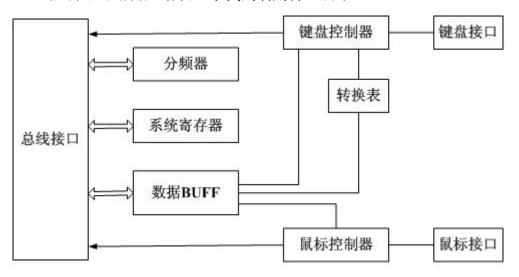

| 20   | PS/2               |                     | 213      |

| 20.1 | PS/2 控制            | 削器结构 <b>错误</b>      | !未定义书签。  |

|      | 20.1.1             | 接口寄存器描述错误           | ! 未定义书签。 |

|      | 20.1.2             | 状态寄存器的位描述:错误        | ! 未定义书签。 |

|      | 20.1.3             | 命令寄存器的位描述错误         | !未定义书签。  |

|      | 20.1.4             | 控制器命令描述错误           | !未定义书签。  |

|      | 20.1.5             | 命令列表 <b>错误</b>      | !未定义书签。  |

| 21   | I2C                |                     | 217      |

| 21.1 |                    | 器结构                 |          |

| 21.2 | I <sup>2</sup> C控制 | 器寄存器说明              |          |

|      | 21.2.1             | 分频锁存器低字节寄存器(PRERIo) | 218      |

|      | 21.2.2             | 分频锁存器高字节寄存器(PRERhi) | 218      |

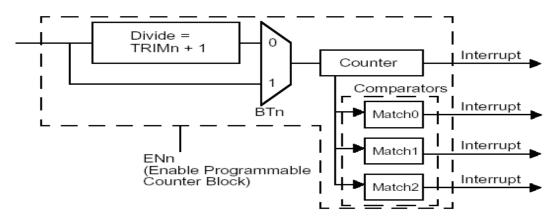

|      | 21.2.3             | 控制寄存器 (CTR)         |          |

|      | 21.2.4             | 发送数据寄存器(TXR)        |          |

|      | 21.2.5             | 接受数据寄存器(RXR)        | _        |

|      | 21.2.6             | 命令控制寄存器(CR)         | 219      |

|      | 21.2.7             | 状态寄存器(SR)           | 219      |

| 22   |                    |                     |          |

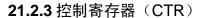

| 22.1 |                    | E调节,计数器,定时器         |          |

| 22.2 |                    | 存器说明                |          |

| 23   |                    |                     |          |

| 23.1 |                    | 图                   |          |

| 23.2 | RTC寄存              | :器描述                | 223      |

| 24    | NAND        |                               |     |  |  |

|-------|-------------|-------------------------------|-----|--|--|

| 24.1  | NAND控制器结构描述 |                               |     |  |  |

| 24.2  | NAND技       | 空制器寄存器配置描述                    |     |  |  |

|       | 24.2.1      | NAND_CMD (地址: BFE7_8000)      | 226 |  |  |

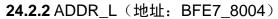

|       | 24.2.2      | ADDR_L(地址: BFE7_8004)         |     |  |  |

|       | 24.2.3      | ADDR_H(地址: BFE7_8008)         | 227 |  |  |

|       | 24.2.4      | NAND_TIMING(地址: BFE7_800C)    | 227 |  |  |

|       | 24.2.5      | ID_L(地址: BFE7_8010)           | 227 |  |  |

|       | 24.2.6      | STATUS & ID_H(地址: BFE7_8014)  | 227 |  |  |

|       | 24.2.7      | NAND_PARAMETER(地址: BFE7_801C) | 227 |  |  |

|       | 24.2.8      | NAND_OP_NUM(地址: BFE7_801C)    | 227 |  |  |

|       | 24.2.9      | CS_RDY_MAP(地址: BFE7_8020)     | 227 |  |  |

| 25    | ACPI        |                               | 229 |  |  |

| 25. 1 | ACPI功耗管理    |                               | 229 |  |  |

|       | 25. 1. 1    | 1F芯片功耗管理概述                    | 229 |  |  |

|       | 25. 1. 2    | 全系统的Power state               | 229 |  |  |

| 25.2  | Godson      | ɪ1F芯片的电源域                     | 232 |  |  |

| 26    | WATCHDOG    |                               |     |  |  |

| 26.1  | WATCH       | [DOG结构说明                      | 233 |  |  |

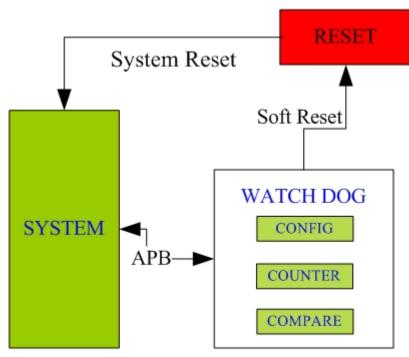

| 26.2  | WATCH       | [DOG寄存器描述                     | 233 |  |  |

|       | 26.2.1      | WDT_EN地址: 0XBFE7_C060)        | 233 |  |  |

|       | 26.2.2      | WDT_SET(地址: 0XBFE7_C064)      | 233 |  |  |

|       | 26.2.3      | WDT_timer(地址: 0XBFE7_C068)    |     |  |  |

| 27    | Clock M     | Management                    | 235 |  |  |

| 27.1  | CLOCK模      | 莫块结构描述                        | 235 |  |  |

| 27.2  | CLOCK質      | 7置描述                          | 235 |  |  |

| 28    | GPIO a      | nd MUX                        | 237 |  |  |

| 28.1  | GPIO结       | 构描述                           | 237 |  |  |

| 28.2  | GPIO寄       | 存器描述                          | 239 |  |  |

| 28.3  |             |                               |     |  |  |

| 29    |             | 13 HI 3HI C                   |     |  |  |

| 29.1  |             | 充                             |     |  |  |

| 29.2  |             | ÿ                             |     |  |  |

### 图目录

| <b>S</b> | 1-1 1F芯片结构图                            | 2  |

|----------|----------------------------------------|----|

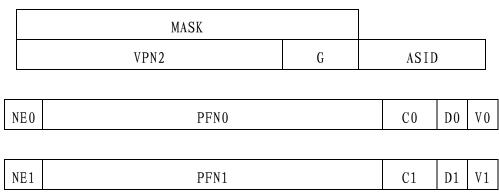

| 图        | 4-1 TLB表项内容                            | 41 |

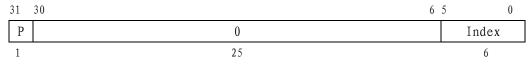

| 图        | 4-2 Index 寄存器                          | 45 |

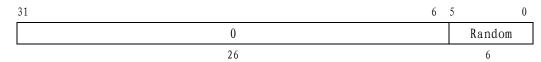

| 图        | 4-3 Random寄存器                          | 46 |

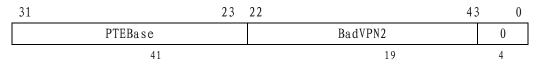

| 图        | 4-4 EntryLo0 和EntryLo1 寄存器             | 46 |

| 图        | 4-5 Context寄存器                         | 47 |

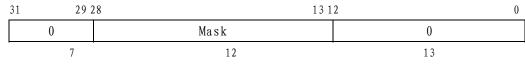

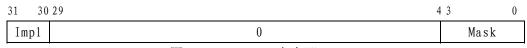

| 图        | 4-6 PageMask寄存器                        | 48 |

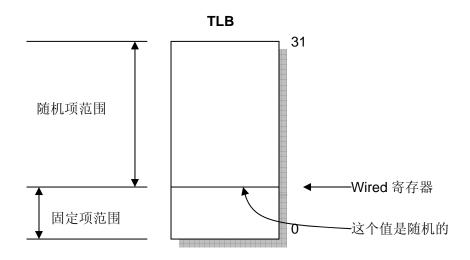

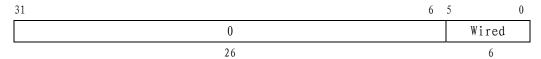

| 图        | 4-7 Wired寄存器界限                         | 49 |

| 冬        | 4-8 Wired寄存器                           | 49 |

| 图        | 4-9 HWREna寄存器                          | 49 |

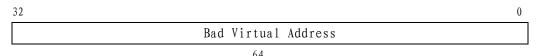

| 图        | 4-10 BadVAddr寄存器                       | 50 |

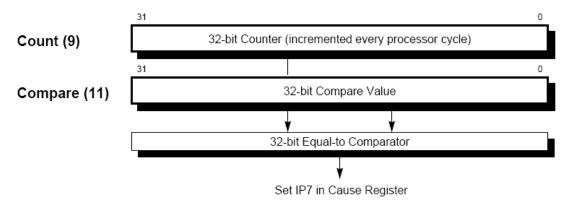

| 图        | 4-11 Count寄存器和Compare寄存器               | 50 |

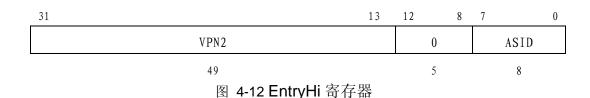

| 图        | 4-12 EntryHi寄存器                        | 51 |

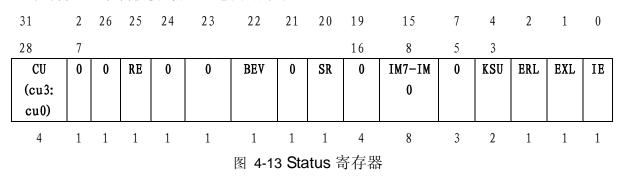

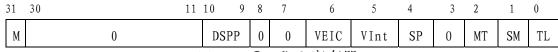

| 图        | 4-13 Status寄存器                         | 51 |

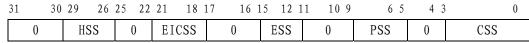

| 图        | 4-14 IntCtl寄存器                         | 53 |

| 图        | 4-15SRSCtl寄存器                          | 54 |

| 图        | 4-16 SRSMap寄存器                         | 54 |

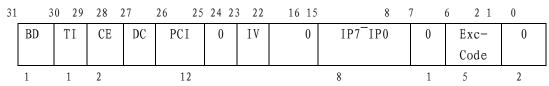

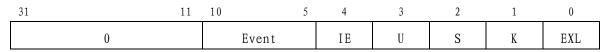

| 图        | 4-17 Cause寄存器                          | 55 |

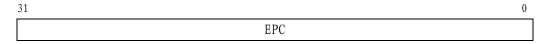

| 图        | 4-18 EPC寄存器                            | 56 |

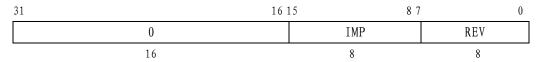

| 图        | 4-19 Processor Revision Identifier 寄存器 | 56 |

| 图        | 4-20 Config寄存器                         | 57 |

| 图        | 4-21 Config1 寄存器                       | 58 |

| 图        | 4-22 Config2 寄存器                       | 59 |

| 图        | 4-23 Config3 寄存器                       | 59 |

| 图        | 4-24 Config6 寄存器                       | 59 |

| 图        | 4-25 WatchLo寄存器                        | 60 |

| 图        | 4-26 WatchHi寄存器                        | 61 |

| 图        | 4-27 控制寄存器性能计数寄存器                      | 61 |

| 图        | 4-28 性能计数器寄存器                          | 61 |

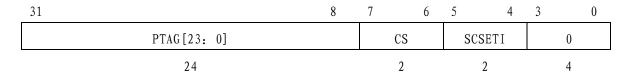

| 图        | 4-29 TagLo 寄存器(P-Cache)                | 63 |

| 图        | 4-30 ErrorEPC寄存器                       | 63 |

| 图        | 4-31 EJTAG调试连接示意图                      | 64 |

| 图        | 4-32 DCR寄存器格式                          | 66 |

| 冬 | 日 4-33 硬件指令、数据断点概况                  | 68        |

|---|-------------------------------------|-----------|

| 图 | 日 4-34 IBS寄存器格式                     | 68        |

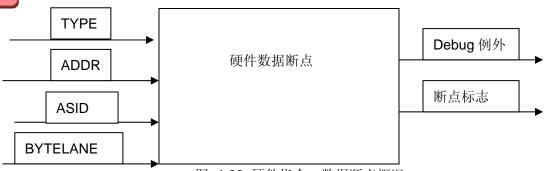

| 图 | 图 4-35 IBAn寄存器格式                    | 69        |

| 图 | 日 4-36 IBMn寄存器格式                    | 69        |

| 图 | 图 4-37 IBCn寄存器格式                    | 69        |

| 图 | 图 4-38 DBS寄存器格式                     | 70        |

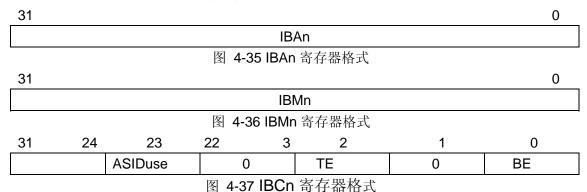

| 图 | 日 4-39 DBAn寄存器格式                    | 71        |

| 图 | 图 4-40 DBMn寄存器格式                    | 71        |

| 图 | 日 4-41 DBCn寄存器格式                    | 71        |

| 图 | 日 4-42 TAP主要部分                      | 76        |

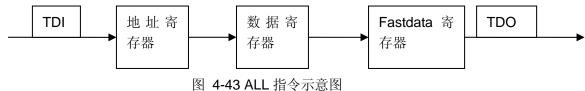

| 图 | 日 4-43 ALL指令示意图                     | 77        |

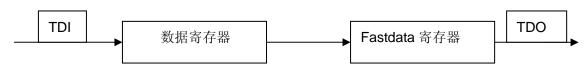

| 图 | 日 4-44 Fastdata 指令示意图               | 78        |

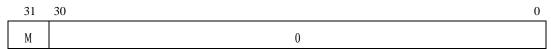

| 图 | 日 4-45 IDCODE寄存器格式                  | 79        |

| 图 | 日 4-46 IMPCADE寄存器示意图                | 79        |

| 图 | 图 4-47 数据寄存器格式                      | 80        |

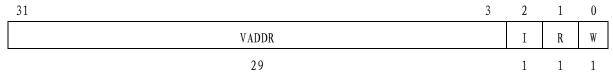

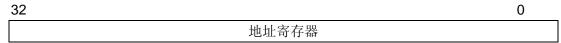

| 图 | 图 4-48 地址寄存器格式                      | 82        |

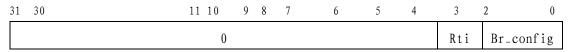

| 图 | 日 4-49 ECR格式                        | 82        |

| 图 | 9-1 DMA 描述符的基本格式(小尾端 32 位总线)        | 吴! 未定义书签。 |

| 图 | 9-2 DMA 描述符的基本格式(小尾端 64 位总线)错记      | 吴! 未定义书签。 |

| 图 | 图 9-3 DMA 接收描述符的基本格式(小尾端 32 位总线)错记  | 吴! 未定义书签。 |

| 图 | 图 10-1 DMA 描述符的基本格式(小尾端 32 位总线)错记   | 吴! 未定义书签。 |

| 图 | 图 10-2 DMA 描述符的基本格式(小尾端 64 位总线)错记   | 吴! 未定义书签。 |

| 图 | 图 10-3 DMA 接收描述符的基本格式(小尾端 32 位总线)错记 | 吴! 未定义书签。 |

| 图 | 图 11-1 SATA系统模块图                    | 163       |

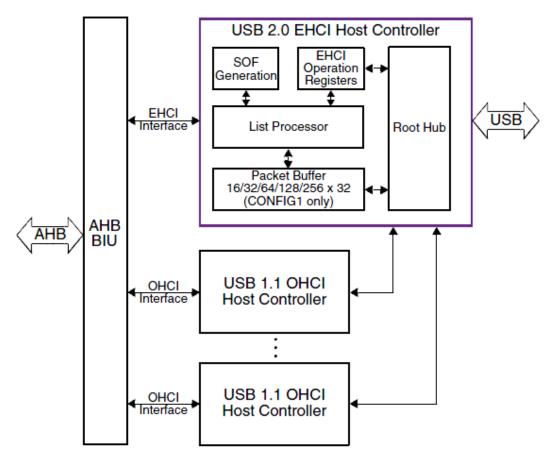

| 图 | 图 12-1 USB主机控制器模块图                  | 166       |

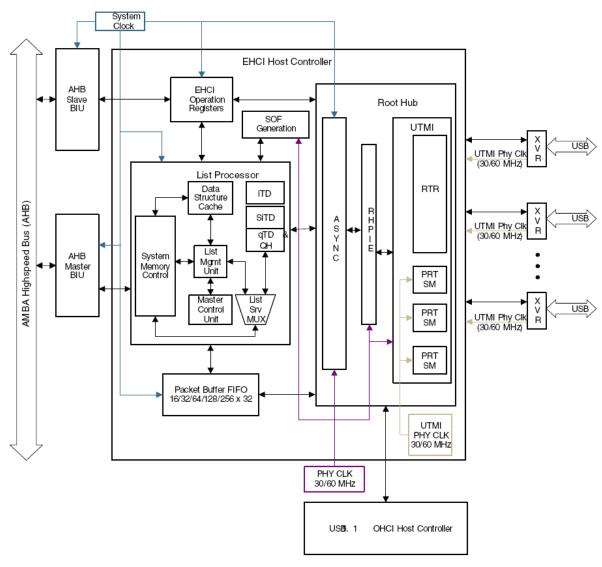

| 图 | 图 12-2 USB主机控制器细节模块图(带EHCI控制器细节).   | 167       |

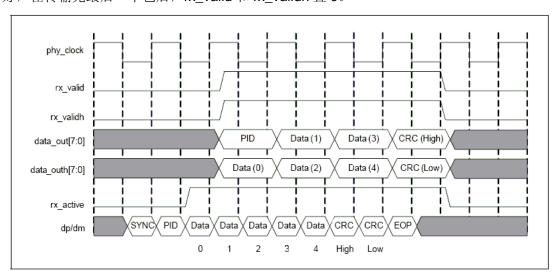

| 图 | 图 12-3 接收时序图(16 bit UTMI接口,偶数个数据)   | 172       |

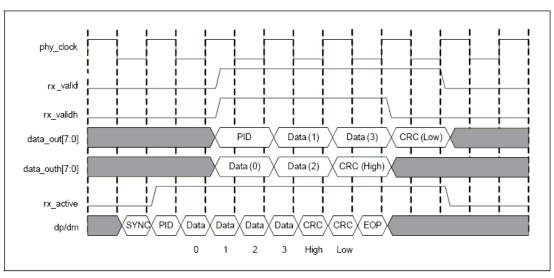

| 图 | 图 12-4 接收时序图(16 bit UTMI接口,奇数个数据)   | 173       |

| 图 | 图 12-5 传输时序图(16 bit UTMI接口,偶数个数据)   | 173       |

| 图 | 图 12-6 传输时序图(16bit UTMI接口,奇数个数据)    | 174       |

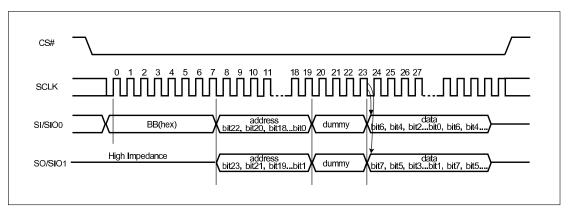

| 图 | 图 13-1 SPI 主控制器结构                   | 176       |

| 图 | 图 14-1 SPI1 主控制器结构 <b>错记</b>        | 吴! 未定义书签。 |

| 图 | 日 17-1 UART控制器结构                    | 192       |

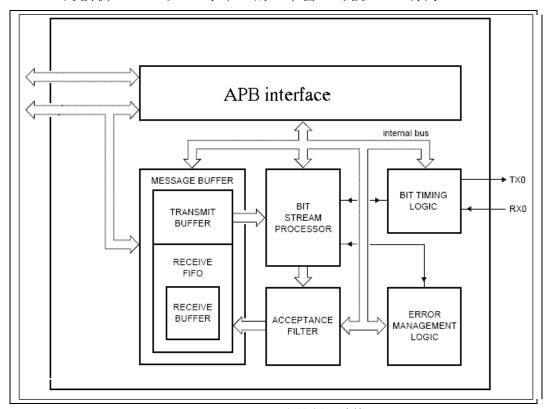

| 图 | 图 18-1 CAN主控制器结构                    | 198       |

| 图 | 19-1 | AC97 应用系统 | 208        |

|---|------|-----------|------------|

|   |      |           | 错误! 未定义书签。 |

| 图 | 23-1 | RTC结构图    | 223        |

| 图 | 26-1 | 看门狗的结构图   | 233        |

| 冬 | 27-1 | 1F 时钟产生模块 | 235        |

### 表目录

| 表 | 2-1 芯片引脚PAD的排布列表             | 9  |

|---|------------------------------|----|

| 表 | 2-2 系统时钟引脚定义                 | 20 |

| 表 | 2-3 LCD引脚定义                  | 20 |

| 表 | 2-4 PLL引脚定义                  | 29 |

| 表 | 2-5 VR引脚定义                   | 21 |

| 表 | 2-6 DDR引脚定义                  | 21 |

| 表 | 2-7 USB引脚定义                  | 23 |

| 表 | 2-8 JTAG引脚定义                 | 24 |

| 表 | 2-9 GMAC0 引脚定义               | 24 |

| 表 | 2-10 GMAC1 引脚定义              | 24 |

| 表 | 2-11 AC97 引脚定义               | 24 |

| 表 | 2-12 SPI引脚定义                 | 25 |

| 表 | 2-13 UART引脚定义                | 25 |

| 表 | 2-14 I2C引脚定义                 | 25 |

| 表 | 2-15 CAN引脚定义                 | 26 |

| 表 | 2-16 NAND flash引脚定义          | 26 |

| 表 | 2-17 PWM引脚定义                 | 26 |

| 表 | 2-18 系统时钟引脚定义                | 26 |

| 表 | 2-19 系统时钟引脚定义                | 26 |

| 表 | 2-20 SATA引脚定义                | 28 |

| 表 | 2-21 ACPI引脚定义                | 28 |

| 表 | 2-22 PS2 引脚定义                | 29 |

| 表 | 2-23 VGA引脚定义                 | 21 |

| 表 | 2-24 电源地引脚                   | 29 |

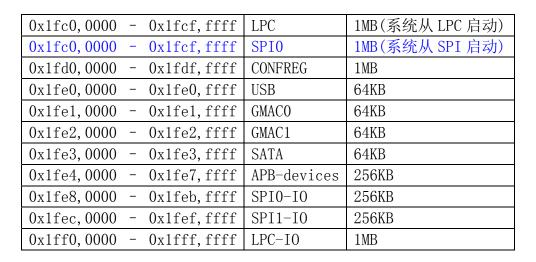

| - | 3-1 AXI各模块地址分配               |    |

| 表 | 3-2 AXI-MUX各模块地址分配           | 31 |

|   | 3-3 APB各模块地址分配               |    |

|   | 4-1 CPU指令集: 访存指令             |    |

| 表 | 4-2 CPU 指令集: 算术指令 (ALU 立即数)  | 36 |

| 表 | 4-3 CPU 指令集: 算术指令 (2 操作数)    | 36 |

| 表 | 4-4 CPU指令集: 算术指令(3 操作数, R-型) | 36 |

| 表 | 4-5 CPU指令集: 乘法和除法指令    | .37 |

|---|------------------------|-----|

| 表 | 4-6 CPU指令集: 跳转和分支指令    | .37 |

| 表 | 4-7 CPU指令集: 移位指令       | .38 |

| 表 | 4-8 CPU指令集: 特殊指令       | .38 |

| 表 | 4-9 CPU指令集: 异常指令       | .38 |

| 表 | 4-10 CPU指令集: CP0 指令    | .39 |

| 表 | 4-11 GS232 的CP0 指令     | .39 |

| 表 | 4-12 GS232IP地址空间的分配    | .40 |

| 表 | 4-13 例外编码及寄存器修改        | .42 |

| 表 | 4-14 例外入口地址            | .43 |

| 表 | 4-15 GS232IP实现的CP0 寄存器 | .44 |

| 表 | 4-16 Index寄存器各域描述      | .45 |

| 表 | 4-17 Random寄存器各域       | .46 |

| 表 | 4-18 EntryLo寄存器域       | .46 |

| 表 | 4-19 Context寄存器域       | .47 |

| 表 | 4-20 不同页大小的掩码(Mask)值   | .48 |

| 表 | 4-21 Wired寄存器域         | .49 |

| 表 | 4-22 HWREna寄存器域        | .49 |

| 表 | 4-23 EntryHi寄存器域       | .51 |

| 表 | 4-24 Status 寄存器域       | .51 |

| 表 | 4-25 IntCtl寄存器域        | .53 |

| 表 | 4-26 SRSCtl寄存器域        | .54 |

| 表 | 4-27Cause寄存器域          | .55 |

| 表 | 4-28 Cause寄存器的ExcCode域 | .55 |

| 表 | 4-29 PRId 寄存器域         | .56 |

| 表 | 4-30 Config0 寄存器域      | .57 |

| 表 | 4-31 Config1 寄存器域      | .58 |

| 表 | 4-32 Config 2 寄存器域     | .59 |

| 表 | 4-33 Config 3 寄存器域     | .59 |

| 表 | 4-34 Config6 寄存器域      | .59 |

| 表 | 4-35 WatchLo寄存器域       | .60 |

| 表 | 4-36 WatchHi寄存器域       | .61 |

| 表 | 4-37 控制域格式             | .62 |

| 表 | 4-38 计数使能位定义           | .62 |

| 表 | 4-39 计数器 0/1 事件               | 62  |

|---|-------------------------------|-----|

| 表 | 4-40 Cache Tag寄存器域            | 63  |

| 表 | 4-41 CP0 指令                   | 63  |

| 表 | 4-42 DCR寄存器域                  | 66  |

| 表 | 4-43 硬件断点寄存器                  | 68  |

| 表 | 4-44 IBS域描述                   | 68  |

| 表 | 4-45 IBCn域描述                  | 69  |

| 表 | 4-46 DBS域描述                   | 70  |

| 表 | 4-47 DBCn域描述                  | 71  |

| 表 | 4-48 调试例外优先级表                 | 73  |

| 表 | 4-49 例外屏蔽表                    | 74  |

| 表 | 4-50 Dseg划分                   | 75  |

| 表 | 4-51 Dmseg的访问情况               | 75  |

| 表 | 4-52 Drseg的访问情况               | 75  |

| 表 | 4-53 调试例外中断入口地址               | 76  |

| 表 | 4-54 EJTAG指令                  | 77  |

| 表 | 4-55 TAP数据寄存器                 | 78  |

| 表 | 4-56 IDCODE寄存器说明              | 79  |

| 表 | 4-57 IMPCODE寄存器说明             | 79  |

| 表 | 4-58 Psz位的含义                  | 81  |

| 表 | 4-59 ECR域描述                   | 82  |

| 表 | 4-60 Sample寄存器说明              | 84  |

| 表 | 5-1 DDR2 SDRAM行/列地址转换         | 85  |

| 表 | 6-1 龙芯 1F访问PCI总线的地址空间划分       | 88  |

| 表 | 6-2 龙芯 1F的PCI控制器pciheader空间划分 | 89  |

| 表 | 6-3 龙芯 1F内部资源在PCI总线上的映射       | 90  |

| 表 | 22-1 寄存器设置                    | 221 |

| 表 | 22-2 寄存器设置                    | 221 |

| 表 | 22-3 主计数器设置                   | 221 |

| 表 | 22-4 高脉冲计数器设置                 | 221 |

| 表 | 22-5 低脉冲计数器设置                 | 221 |

| 表 | 22-6 控制寄存器设置                  | 222 |

| 表 | 29-1 1F电源域                    | 241 |

| 表 | 29-2 上电配置引脚汇总                 | 241 |

### 1 概述

1F 芯片是基于 GS232 处理器核的高性价比单芯片系统,可广泛应用于工业控制、家庭网关、信息家电、医疗器械和安全应用等领域。1F 用 SMIC 0.13 微米工艺实现,采用 Wire Bond BGA448 封装。

1F 片具有以下关键特性:

- 集成一个 GS232 双发射龙芯处理器核,指令和数据 L1 Cache 各 16KB

- 集成 2D GPU

- 集成两路 DC 控制器,最大分辨率可支持到 1920\*1080@60Hz/24bit

- 集成2个10M/100M/1000M 自适应GMAC

- 集成2个SATA2

- 集成 32 位 PCI, 支持主从模式

- 集成 1 个 32 位 DDR2 控制器

- 集成 4 个 USB HOST 接口, 兼容 USB2. 0 和 USB1. 1

- 集成1个8位 NAND FLASH 控制器, 最大支持 32GB

- 集成中断控制器,支持灵活的中断设置

- 集成2个SPI控制器,支持主模式,SPI0支持系统启动

- 集成 AC97 控制器

- 集成 4 位 LPC 控制器

- 集成4路UART串口

- 集成1路PS2

- 集成 3 路 I2C 控制器, 兼容 SMBUS

- 集成 2 路 CAN 总线控制器

- 集成 88 路 GPIO 端口

- 集成 1 路 RTC 接口

- 集成4路PWM控制器

- 集成 ACPI

- 集成看门狗电路

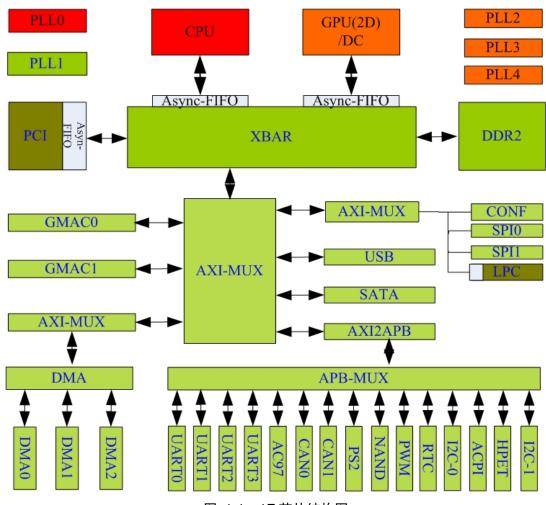

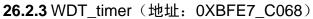

#### 1.1 体系结构框图

1F 芯片内部顶层结构由 AXI 交叉开关互连,其中 GS232、GPU/DC、PCI 和 AXI\_MUX 作为主设备通过 4X4 交叉开关连接到系统; GPU/DC、AXI\_MUX、PCI 和 DDR2 作为从设备通过 4X4 交叉开关连接到系统。在 AXI\_MUX 内部实现了多个 AHB 和 APB 模块到顶层 AXI 交叉开关的连接,其中 DMA\_MUX、GMACO、GMAC1、USB 和 SATA 被 AXI\_MUX 选择作为主设备访问交叉开关; AXI\_MUX(包括 confreg、SPI0、SPI1)、 AXI2APB、SATA、GMACO、GMAC1、USB 等作为从设备被来自 AXI\_MUX 的 主设备访问。在 AXI2APB 内部实现了系统对内部 APB 接口设备的访问,这些设备包括 Watch Dog、RTC、PWM、I2C、PS2、CAN、NAND、UART等。

图 1-1 1F 芯片结构图

#### 1.2 芯片主要功能

1F 芯片支持以下功能:

#### 1.2.1 GS232 CPU

龙芯 232 核是一款实现 MIPS32 兼容且支持 EJTAG 调试的双发射处理器,通

过采用转移预测、寄存器重命名、乱序发射、路预测的指令CACHE、非阻塞的数据 CACHE、写合并收集等技术来提高流水线的效率。

- 双发射五级流水、乱序发射、乱序执行

- 16KB 指令 Cache+16KB 数据 Cache, 4 路组相连, 指令 CACHE 支持路预测

- 6项 BRQ、16 项的 QUEUE

- 动态转移预测、地址返回栈

- 32项 JTLB, 4项 ITLB、8项 DTLB

- 两个定点 ALU 部件。

- 浮点部件支持全流水的64位浮点加法和浮点乘法运算,硬件实现浮点除法运算。

- 专门的 SIMD 型多媒体加速指令。

- 支持非阻塞的 Cache 访问技术, 4 项 load 队列、2 项 store 队列、3 项 miss 队列, 最多容忍 5 条 store 指令 Cache 不命中和 4 条 load 指令 Cache 不命中。

- 支持 cached store 指令的写合并

- 支持预取指令

- 支持流水线暂停模式

- 支持向量中断,可配置支持快速中断响应,最多8个时钟周期进入中断处理程序

- 支持 EJTAG 调试, 6 个指令断点、2 个数据断点

#### **1.2.2** DDR2

- 32 位 DDR2 控制器

- 遵守 DDR2 DDR 的行业标准(JESD79-2B)

- 支持最大 2 个物理内存 bank (由 2 个 DDR2 DDR 片选信号实现),一共含有 18 位的地址总线(即: 15 位的行列地址总线和 3 位的逻辑 Bank 总线)。

- 接口上命令、读写数据全流水操作

- 内存命令合并、排序提高整体带宽

- 配置寄存器读写端口,可以修改内存设备的基本参数

- 内建动态延迟补偿电路(DCC),用于数据的可靠发送和接收

- 支持 133-233MHZ 工作频率

#### **1.2.3** PCI

- PCI 2.2/PCIX 兼容, 32 位总线宽度, 支持 66MHz 总线频率

- 既可以做 Host (SoC), 又可以做 Device (南桥), 上电时由外面 PAD 配置

- 作为 Host 最多支持 2 个 PCI 设备

- 作为 Device 时有三个 PCI 地址窗口: IO、Memory、Prefetchable Memory。其中 Prefetchable Memory 窗口用来访问片上 DDR2。

#### 1.2.4 2D GPU

- 通过 Futuremark 认证

- 动态电源管理

- 支持 BitBLT 和 Stretch BLT

- 矩形填充

- 硬件画线

- 单色字体渲染

- ROP2, ROP3, ROP4

- Alpha 混合

- 32Kx32K 坐标系统

- 90 度旋转

- 透明支持

- YUV 色域空间转换

#### 1.2.5 LCD Controller

- 屏幕大小可达 1920\*1080

- 硬件光标

- 伽玛校正

- 最高像素时钟 172MHz

- 支持线性显示缓冲

- 上电序列控制

• 具有 VGA 和 DVI 双接口; 16 位, 24 位支持

#### **1.2.6** SATA

- 2 个独立 SATA2 的接口

- 支持 SATA 1 代 1.5Gbps 和 SATA2 代 3Gbps 的传输

- 兼容串行 ATA 2.6 规范和 AHCI 1.1 规范

#### 1.2.7 USB2.0

- 4 个独立的 USB2. 0 的 HOST ports 及 PHY

- 兼容 USB1.1 和 USB2.0

- 内部 EHCI 控制和实现高速传输可达 480Mbps

- 内部 OHCI 控制和实现全速和低速传输 12Mbps 和 1.5Mbps

#### **1.2.8** AC97

- 支持 16, 18 和 20 位采样精度,支持可变速率

- 最高达 48KHz

- 2 频道立体声输出

- 支持麦克风输入

#### 1.2.9 GMAC

- 两路 10/100/1000Mbps 自适应以太网控制器

- 双网卡均兼容 IEEE 802.3

- 对外部 PHY 实现 RGMII 和 MII 接口

- 半双工/全双工自适应

- 半双工时,支持碰撞检测与重发(CSMA/CD)协议

- 支持 CRC 校验码的自动生成与校验

#### **1.2.10** LPC

- 兼容 LPC Rev1.1 标准

- 内置 FIF0

#### **1.2.11** SPI

- 支持2路SPI接口

- 支持系统启动

- 极性和相位可编程的串行时钟

- 可在等待模式下对 SPI 进行控制

#### **1.2.12** UART

- 集成1个全功能串口、3个两线串口

- 在寄存器与功能上兼容 NS16550A

- 全双工异步数据接收/发送

- 可编程的数据格式

- 16 位可编程时钟计数器

- 支持接收超时检测

- 带仲裁的多中断系统

#### **1.2.13** I<sup>2</sup>C

- 兼容 SMBUS (100Kbps)

- 与 PHILIPS I2C 标准相兼容

- 只实现主设备操作

- 能够支持多主设备的总线

- 总线的时钟频率可编程

- 可以产生开始/停止/应答等操作

- 能够对总线的状态进行探测

- 支持低速和快速模式

- 支持7位寻址和10位寻址

- 支持时钟延伸和等待状态

#### **1.2.14** PWM

- 提供 4 路可配置 PWM 输出

- 数据宽度 24 位

- 定时器功能

- 计数器功能

- NAND FLASH 最大支持 32GB

- 数据宽度 8bit

#### **1.2.16** CAN

- 支持 2 个独立 CAN 总线接口

- 每路 CAN 接口均支持 CAN2. OA/B 协议

- 支持 CAN 协议扩展

#### 1.2.17 RTC

- 计时精确到 0.1 秒

- 可产生3个计时中断

- 支持定时开关机功能

#### **1.2.18** GPIO

- 88路GPI0

- 支持位操作

#### 1.2.19 INT controller

- 支持软件设置中断

- 支持电平与边沿触发

- 支持中断屏蔽与使能

#### **1.2.20** PS2

- 16 位可编程 5us 时钟计数器,8 位可编程 60us 时钟计数器

- 兼容第一套和第二套键盘扫描码

- 支持编码键盘和非编码键盘

- 支持二键式、三键式鼠标

#### 1.2.21 Watchdog

- 16 位计数器

- 低功耗模式暂停功能

#### **1.2.22** ACPI

- 兼容 ACPI 功耗管理规范

- 各个模块运行频率可调

- 多电压域设计(Core、RTC、Resume)

- 全芯片 Clock gating

- 支持 STR,STD 等睡眠模式

#### 1.2.23 其它

• 测试访问口控制器 JTAG

## 2 芯片引脚定义

#### 2.1 1F 引脚分布图

1F 采用 BGA448 封装形式,芯片的引脚 PAD 的排布列如下表所示:

表 2-1 芯片引脚 PAD 的排布列表

| Pin Number | Net Name      | X Coord   | Y Coord  |

|------------|---------------|-----------|----------|

| A01        | DDR2_A05      | -10500.00 | 10500.00 |

| A02        | DDR2_A00      | -9500.00  | 10500.00 |

| A03        | DDR2_A07      | -8500.00  | 10500.00 |

| A04        | DDR2_A09      | -7500.00  | 10500.00 |

| A05        | DDR2_CKP0     | -6500.00  | 10500.00 |

| A06        | DDR2_CKP1     | -5500.00  | 10500.00 |

| A07        | DDR2_GATE01   | -4500.00  | 10500.00 |

| A08        | DDR2_BA0      | -3500.00  | 10500.00 |

| A09        | DDR2_WEN      | -2500.00  | 10500.00 |

| A10        | DDR2_DQ16     | -1500.00  | 10500.00 |

| A11        | DDR2_DQS2     | -500.00   | 10500.00 |

| A12        | DDR2_DQ17     | 500.00    | 10500.00 |

| A13        | DDR2_DQ22     | 1500.00   | 10500.00 |

| A14        | GMACO_RX_CTL  | 2500.00   | 10500.00 |

| A15        | GMACO_RX2     | 3500.00   | 10500.00 |

| A16        | RSM_ACPI_EN   | 4500.00   | 10500.00 |

| A17        | ACPI_SYS_RSTN | 5500.00   | 10500.00 |

| A18        | PLL_1_AVSS33  | 6500.00   | 10500.00 |

| A19        | PLL_1_AVDD33  | 7500.00   | 10500.00 |

| A20        | PLL_1_AVSS33  | 8500.00   | 10500.00 |

| A21        | PLL_1_AVDD33  | 9500.00   | 10500.00 |

| A22        | RTC_CLK_I     | 10500.00  | 10500.00 |

| B01        | DDR2_A06      | -10500.00 | 9500.00  |

| B02        | DDR2_A01      | -9500.00  | 9500.00  |

| В03        | DDR2_A08      | -8500.00  | 9500.00  |

| B04        | DDR2_A10      | -7500.00  | 9500.00  |

| В05        | DDR2_CKN0     | -6500.00  | 9500.00  |

| В06        | DDR2_CKN1     | -5500.00  | 9500.00  |

| В07        | DDR2_ODT0     | -4500.00  | 9500.00  |

| В08        | DDR2_BA1      | -3500.00  | 9500.00  |

| В09        | DDR2_SCSN0    | -2500.00  | 9500.00  |

| B10        | DDR2_DQ18     | -1500.00  | 9500.00  |

| B11        | DDR2_DQ23     | -500.00   | 9500.00  |

| B12 | DDR2 DQ20      | 500.00    | 9500.00 |

|-----|----------------|-----------|---------|

| B13 | DDR2 DQM2      | 1500.00   | 9500.00 |

| B14 | GMACO RXO      | 2500.00   | 9500.00 |

| B15 | GMACO RX3      | 3500.00   | 9500.00 |

| B16 | XTALO          | 4500.00   | 9500.00 |

| B17 | RTC VR PD      | 5500.00   | 9500.00 |

| B18 | RTC RTCRSTN    | 6500.00   | 9500.00 |

| B19 | RTC RSMRSTN    | 7500.00   | 9500.00 |

| B20 | RTC_PWROK      | 8500.00   | 9500.00 |

| B21 | ACPI_SOC_EN    | 9500.00   | 9500.00 |

| B22 | RTC_CLK_O      | 10500.00  | 9500.00 |

| C01 | DDR2_A03       | -10500.00 | 8500.00 |

| C02 | DDR2_A02       | -9500.00  | 8500.00 |

| C03 | DDR2_CKE1      | -8500.00  | 8500.00 |

| C04 | DDR2_A11       | -7500.00  | 8500.00 |

| C05 | DDR2_A12       | -6500.00  | 8500.00 |

| C06 | DDR2_GATE00    | -5500.00  | 8500.00 |

| C07 | DDR2_ODT1      | -4500.00  | 8500.00 |

| C08 | DDR2_BA2       | -3500.00  | 8500.00 |

| C09 | DDR2_SCSN1     | -2500.00  | 8500.00 |

| C10 | DDR2_DQ21      | -1500.00  | 8500.00 |

| C11 | VSS            | -500.00   | 8500.00 |

| C12 | DDR2_DQ19      | 500.00    | 8500.00 |

| C13 | VSS            | 1500.00   | 8500.00 |

| C14 | GMACO_RX1      | 2500.00   | 8500.00 |

| C15 | GMACO_RX_CLK_I | 3500.00   | 8500.00 |

| C16 | XTALI          | 4500.00   | 8500.00 |

| C17 | VSS            | 5500.00   | 8500.00 |

| C18 | RTC_VDD3V3     | 6500.00   | 8500.00 |

| C19 | RTC_VR_CEXT    | 7500.00   | 8500.00 |

| C20 | RTC_VR_VOUT    | 8500.00   | 8500.00 |

| C21 | RSM_S3N        | 9500.00   | 8500.00 |

| C22 | RSM_S4N        | 10500.00  | 8500.00 |

| D01 | DDR2_A04       | -10500.00 | 7500.00 |

| D02 | DDR2_A14       | -9500.00  | 7500.00 |

| D03 | VSS            | -8500.00  | 7500.00 |

| D04 | VSS            | -7500.00  | 7500.00 |

| D05 | DDR2_A13       | -6500.00  | 7500.00 |

| D06 | DDR2_GATE10    | -5500.00  | 7500.00 |

| D07 | DDR2_CKE0      | -4500.00  | 7500.00 |

| D08 | DDR2_RASN      | -3500.00  | 7500.00 |

| D09 | DDR2_DQ26      | -2500.00  | 7500.00 |

| D10 | DDR2_DQ31      | -1500.00  | 7500.00 |

| D11 | DDR2_DQM3      | -500.00   | 7500.00 |

|-----|----------------|-----------|---------|

| D12 | DDR2 DQ25      | 500.00    | 7500.00 |

| D13 | DDR2 DQ28      | 1500.00   | 7500.00 |

| D14 | GMACO TX CLK O | 2500.00   | 7500.00 |

| D15 | GMACO TX2      | 3500.00   | 7500.00 |

| D16 | GMACO MDCK     | 4500.00   | 7500.00 |

| D17 | RTC_VDD3V3     | 5500.00   | 7500.00 |

| D18 | VSS            | 6500.00   | 7500.00 |

| D19 | RTC_VR_VBG     | 7500.00   | 7500.00 |

| D20 | RSM_PWRBTNN    | 8500.00   | 7500.00 |

| D21 | RSM_RIN        | 9500.00   | 7500.00 |

| D22 | RSM_REBOOTN    | 10500.00  | 7500.00 |

| E01 | DDR2_DQM0      | -10500.00 | 6500.00 |

| E02 | DDR2_DQ06      | -9500.00  | 6500.00 |

| E03 | DDR2_DQ11      | -8500.00  | 6500.00 |

| E04 | DDR2_DQ12      | -7500.00  | 6500.00 |

| E05 | DDR2_DQ09      | -6500.00  | 6500.00 |

| E06 | DDR2_GATEI1    | -5500.00  | 6500.00 |

| E07 | VDD1V8         | -4500.00  | 6500.00 |

| E08 | DDR2_CASN      | -3500.00  | 6500.00 |

| E09 | DDR2_DQ29      | -2500.00  | 6500.00 |

| E10 | DDR2_DQ24      | -1500.00  | 6500.00 |

| E11 | DDR2_DQS3      | -500.00   | 6500.00 |

| E12 | DDR2_DQ30      | 500.00    | 6500.00 |

| E13 | DDR2_DQ27      | 1500.00   | 6500.00 |

| E14 | GMACO_TXO      | 2500.00   | 6500.00 |

| E15 | GMACO_TX3      | 3500.00   | 6500.00 |

| E16 | GMACO_MDIO     | 4500.00   | 6500.00 |

| E17 | VSS            | 5500.00   | 6500.00 |

| E18 | RSM_SUS_STATN  | 6500.00   | 6500.00 |

| E19 | RSM_PMEN       | 7500.00   | 6500.00 |

| E20 | RSM_LID        | 8500.00   | 6500.00 |

| E21 | SATAO_TXP      | 9500.00   | 6500.00 |

| E22 | SATAO_TXN      | 10500.00  | 6500.00 |

| F01 | DDR2_DQ03      | -10500.00 | 5500.00 |

| F02 | DDR2_DQ04      | -9500.00  | 5500.00 |

| F03 | DDR2_DQ01      | -8500.00  | 5500.00 |

| F04 | DDR2_DQM1      | -7500.00  | 5500.00 |

| F05 | DDR2_DQ14      | -6500.00  | 5500.00 |

| F06 | VDD1V8         | -5500.00  | 5500.00 |

| F07 | VDD1V8         | -4500.00  | 5500.00 |

| F08 | VDD1V8         | -3500.00  | 5500.00 |

| F09 | VDD1V8         | -2500.00  | 5500.00 |

| F10 | VREF 0V9       | -1500.00  | 5500.00 |

|-----|----------------|-----------|---------|

| F11 | VSS            | -500.00   | 5500.00 |

| F12 | VSS            | 500.00    | 5500.00 |

| F13 | VREF_0V9       | 1500.00   | 5500.00 |

| F14 | GMACO TX1      | 2500.00   | 5500.00 |

| F15 | GMACO_TX_CTL   | 3500.00   | 5500.00 |

| F16 | GMACO_TX_CLK_I | 4500.00   | 5500.00 |

| F17 | RSM_VDD3V3     | 5500.00   | 5500.00 |

| F18 | RSM_BATLOWN    | 6500.00   | 5500.00 |

| F19 | SATA_VSS       | 7500.00   | 5500.00 |

| F20 | SATA_VDD3V3    | 8500.00   | 5500.00 |

| F21 | SATAO_RXN      | 9500.00   | 5500.00 |

| F22 | SATAO_RXP      | 10500.00  | 5500.00 |

| G01 | DDR2_DQ07      | -10500.00 | 4500.00 |

| G02 | DDR2_DQS0      | -9500.00  | 4500.00 |

| G03 | DDR2_DQ08      | -8500.00  | 4500.00 |

| G04 | DDR2_DQ15      | -7500.00  | 4500.00 |

| G05 | DDR2_DQS1      | -6500.00  | 4500.00 |

| G06 | VDD1V8         | -5500.00  | 4500.00 |

| G17 | VSS            | 5500.00   | 4500.00 |

| G18 | RSM_VDD1V2     | 6500.00   | 4500.00 |

| G19 | SATA_RESREF    | 7500.00   | 4500.00 |

| G20 | SATA1_TXP      | 8500.00   | 4500.00 |

| G21 | SATA1_TXN      | 9500.00   | 4500.00 |

| G22 | SATA_REFCLKN   | 10500.00  | 4500.00 |

| H01 | DDR2_DQ05      | -10500.00 | 3500.00 |

| Н02 | DDR2_DQ02      | -9500.00  | 3500.00 |

| Н03 | DDR2_DQ00      | -8500.00  | 3500.00 |

| Н04 | DDR2_DQ13      | -7500.00  | 3500.00 |

| H05 | DDR2_DQ10      | -6500.00  | 3500.00 |

| Н06 | VREF_0V9       | -5500.00  | 3500.00 |

| Н08 | VSS            | -3500.00  | 3500.00 |

| Н09 | VDD1V8         | -2500.00  | 3500.00 |

| H10 | VSS            | -1500.00  | 3500.00 |

| H11 | VDD1V8         | -500.00   | 3500.00 |

| H12 | VSS            | 500.00    | 3500.00 |

| H13 | VDD1V8         | 1500.00   | 3500.00 |

| H14 | VSS            | 2500.00   | 3500.00 |

| H15 | VDD3V3         | 3500.00   | 3500.00 |

| H17 | USB_VDD1V2     | 5500.00   | 3500.00 |

| H18 | SATA_VDD1V2    | 6500.00   | 3500.00 |

| H19 | SATA_VSS       | 7500.00   | 3500.00 |

| H20 | SATA1_RXN      | 8500.00   | 3500.00 |

| H21 | SATA1_RXP    | 9500.00   | 3500.00 |

|-----|--------------|-----------|---------|

| H22 | SATA_REFCLKP | 10500.00  | 3500.00 |

| Ј01 | VDD1V2       | -10500.00 | 2500.00 |

| Ј02 | VSS          | -9500.00  | 2500.00 |

| Ј03 | VDD1V2       | -8500.00  | 2500.00 |

| J04 | VSS          | -7500.00  | 2500.00 |

| Ј05 | VDD1V2       | -6500.00  | 2500.00 |

| Ј06 | VSS          | -5500.00  | 2500.00 |

| Ј08 | VDD1V8       | -3500.00  | 2500.00 |

| Ј09 | VSS          | -2500.00  | 2500.00 |

| Ј10 | VDD1V8       | -1500.00  | 2500.00 |

| J11 | VSS          | -500.00   | 2500.00 |

| J12 | VDD1V8       | 500.00    | 2500.00 |

| Ј13 | VSS          | 1500.00   | 2500.00 |

| J14 | VDD3V3       | 2500.00   | 2500.00 |

| J15 | VSS          | 3500.00   | 2500.00 |

| J17 | USB_VSS      | 5500.00   | 2500.00 |

| Ј18 | USB0_REXT    | 6500.00   | 2500.00 |

| Ј19 | USBO_DP      | 7500.00   | 2500.00 |

| Ј20 | USBO_DM      | 8500.00   | 2500.00 |

| J21 | USB0_X0      | 9500.00   | 2500.00 |

| J22 | USBO_XI      | 10500.00  | 2500.00 |

| K01 | VSS          | -10500.00 | 1500.00 |

| K02 | VDD1V2       | -9500.00  | 1500.00 |

| К03 | VSS          | -8500.00  | 1500.00 |

| K04 | VDD1V2       | -7500.00  | 1500.00 |

| K05 | VSS          | -6500.00  | 1500.00 |

| K06 | VDD1V2       | -5500.00  | 1500.00 |

| K08 | VSS          | -3500.00  | 1500.00 |

| K09 | VDD1V2       | -2500.00  | 1500.00 |

| K10 | VSS          | -1500.00  | 1500.00 |

| K11 | VDD1V2       | -500.00   | 1500.00 |

| K12 | VSS          | 500.00    | 1500.00 |

| K13 | VDD3V3       | 1500.00   | 1500.00 |

| K14 | VSS          | 2500.00   | 1500.00 |

| K15 | VDD3V3       | 3500.00   | 1500.00 |

| K17 | USB_VDD1V2   | 5500.00   | 1500.00 |

| K18 | USB1_REXT    | 6500.00   | 1500.00 |

| K19 | USB1_DP      | 7500.00   | 1500.00 |

| K20 | USB1_DM      | 8500.00   | 1500.00 |

| K21 | USB1_X0      | 9500.00   | 1500.00 |

| K22 | USB1_XI      | 10500.00  | 1500.00 |

| L01 | PCI_AD02     | -10500.00 | 500.00  |

| L02 | PCI AD03   | -9500.00  | 500.00   |

|-----|------------|-----------|----------|

| L03 | PCI AD04   | -8500.00  | 500.00   |

| L04 | PCI AD00   | -7500.00  | 500.00   |

| L05 | PCI AD01   | -6500, 00 | 500.00   |

| L06 | VSS        | -5500.00  | 500.00   |

| L08 | VDD1V2     | -3500.00  | 500.00   |

| L09 | VSS        | -2500.00  | 500.00   |

| L10 | VDD1V2     | -1500.00  | 500.00   |

| L11 | VSS        | -500.00   | 500.00   |

| L12 | VDD3V3     | 500.00    | 500.00   |

| L13 | VSS        | 1500.00   | 500.00   |

| L14 | VDD3V3     | 2500.00   | 500.00   |

| L15 | VSS        | 3500.00   | 500.00   |

| L17 | USB_VSS    | 5500.00   | 500.00   |

| L18 | USB_AVSS33 | 6500.00   | 500.00   |

| L19 | USB_AVDD33 | 7500.00   | 500.00   |

| L20 | USB_AVSS33 | 8500.00   | 500.00   |

| L21 | USB_AVDD33 | 9500.00   | 500.00   |

| L22 | USB_AVSS33 | 10500.00  | 500.00   |

| MO1 | PCI_AD07   | -10500.00 | -500.00  |

| M02 | PCI_CBEN0  | -9500.00  | -500.00  |

| M03 | PCI_AD08   | -8500.00  | -500.00  |

| M04 | PCI_AD05   | -7500.00  | -500.00  |

| M05 | PCI_AD06   | -6500.00  | -500.00  |

| M06 | VDD3V3     | -5500.00  | -500.00  |

| M08 | VSS        | -3500.00  | -500.00  |

| M09 | VDD1V2     | -2500.00  | -500.00  |

| M10 | VSS        | -1500.00  | -500.00  |

| M11 | VDD1V2     | -500.00   | -500.00  |

| M12 | VSS        | 500.00    | -500.00  |

| M13 | VDD3V3     | 1500.00   | -500.00  |

| M14 | VSS        | 2500.00   | -500.00  |

| M15 | VDD3V3     | 3500.00   | -500.00  |

| M17 | USB_AVDD33 | 5500.00   | -500.00  |

| M18 | USB2_REXT  | 6500.00   | -500.00  |

| M19 | USB2_DP    | 7500.00   | -500.00  |

| M20 | USB2_DM    | 8500.00   | -500.00  |

| M21 | USB2_X0    | 9500.00   | -500.00  |

| M22 | USB2_XI    | 10500.00  | -500.00  |

| N01 | PCI_AD12   | -10500.00 | -1500.00 |

| N02 | PCI_AD13   | -9500.00  | -1500.00 |

| N03 | PCI_AD14   | -8500.00  | -1500.00 |

| N04 | PCI_AD09   | -7500.00  | -1500.00 |

| N05 | PCI_AD10      | -6500.00  | -1500.00 |

|-----|---------------|-----------|----------|

| N06 | PCI_AD11      | -5500.00  | -1500.00 |

| N08 | VDD1V2        | -3500.00  | -1500.00 |

| N09 | VSS           | -2500.00  | -1500.00 |

| N10 | VDD1V2        | -1500.00  | -1500.00 |

| N11 | VSS           | -500.00   | -1500.00 |

| N12 | VDD3V3        | 500.00    | -1500.00 |

| N13 | VSS           | 1500.00   | -1500.00 |

| N14 | VDD3V3        | 2500.00   | -1500.00 |

| N15 | VSS           | 3500.00   | -1500.00 |

| N17 | USB_AVSS33    | 5500.00   | -1500.00 |

| N18 | USB3_REXT     | 6500.00   | -1500.00 |

| N19 | USB3_DP       | 7500.00   | -1500.00 |

| N20 | USB3_DM       | 8500.00   | -1500.00 |

| N21 | USB3_X0       | 9500.00   | -1500.00 |

| N22 | USB3_XI       | 10500.00  | -1500.00 |

| P01 | PCI_PAR       | -10500.00 | -2500.00 |

| P02 | PCI_SERR      | -9500.00  | -2500.00 |

| P03 | PCI_PERR      | -8500.00  | -2500.00 |

| P04 | PCI_AD15      | -7500.00  | -2500.00 |

| P05 | PCI_CBEN1     | -6500.00  | -2500.00 |

| P06 | VSS           | -5500.00  | -2500.00 |

| P08 | VSS           | -3500.00  | -2500.00 |

| P09 | VDD3V3        | -2500.00  | -2500.00 |

| P10 | VSS           | -1500.00  | -2500.00 |

| P11 | VDD3V3        | -500.00   | -2500.00 |

| P12 | VSS           | 500.00    | -2500.00 |

| P13 | VDD3V3        | 1500.00   | -2500.00 |

| P14 | VSS           | 2500.00   | -2500.00 |

| P15 | VDD3V3        | 3500.00   | -2500.00 |

| P17 | USB_AVDD33    | 5500.00   | -2500.00 |

| P18 | USB3_OVRCUR   | 6500.00   | -2500.00 |

| P19 | USB2_OVRCUR   | 7500.00   | -2500.00 |

| P20 | USB1_OVRCUR   | 8500.00   | -2500.00 |

| P21 | USB0_OVRCUR   | 9500.00   | -2500.00 |

| P22 | TEST_JTAG_SEL | 10500.00  | -2500.00 |

| R01 | PCI_TRDYN     | -10500.00 | -3500.00 |

| R02 | PCI_IRDYN     | -9500.00  | -3500.00 |

| R03 | PCI_FRAMEN    | -8500.00  | -3500.00 |

| R04 | PCI_STOPN     | -7500.00  | -3500.00 |

| R05 | PCI_DEVSELN   | -6500.00  | -3500.00 |

| R06 | VDD3V3        | -5500.00  | -3500.00 |

| R08 | VDD3V3        | -3500.00  | -3500.00 |

| R09 | VSS             | -2500.00  | -3500.00 |

|-----|-----------------|-----------|----------|

| R10 | VDD3V3          | -1500.00  | -3500.00 |

| R11 | VSS             | -500.00   | -3500.00 |

| R12 | VDD3V3          | 500.00    | -3500.00 |

| R13 | VSS             | 1500.00   | -3500.00 |

| R14 | VDD3V3          | 2500.00   | -3500.00 |

| R15 | VSS             | 3500.00   | -3500.00 |

| R17 | EJTAG_TRST      | 5500.00   | -3500.00 |

| R18 | EJTAG_TDO       | 6500.00   | -3500.00 |

| R19 | EJTAG_TDI       | 7500.00   | -3500.00 |

| R20 | EJTAG_TCK       | 8500.00   | -3500.00 |

| R21 | EJTAG_TMS       | 9500.00   | -3500.00 |

| R22 | INTN1           | 10500.00  | -3500.00 |

| T01 | PCI_AD18        | -10500.00 | -4500.00 |

| T02 | PCI_AD19        | -9500.00  | -4500.00 |

| T03 | PCI_AD20        | -8500.00  | -4500.00 |

| T04 | PCI_CBEN2       | -7500.00  | -4500.00 |

| T05 | PCI_AD16        | -6500.00  | -4500.00 |

| T06 | PCI_AD17        | -5500.00  | -4500.00 |

| T17 | TEST_BIST_CLK   | 5500.00   | -4500.00 |

| T18 | TEST_CFG_MODEN  | 6500.00   | -4500.00 |

| T19 | TEST_PHY_CLK    | 7500.00   | -4500.00 |

| T20 | TEST_SCAN_MODEN | 8500.00   | -4500.00 |

| T21 | INTNO           | 9500.00   | -4500.00 |

| T22 | PWM3            | 10500.00  | -4500.00 |

| U01 | PCI_AD23        | -10500.00 | -5500.00 |

| U02 | PCI_CBEN3       | -9500.00  | -5500.00 |

| U03 | PCI_AD24        | -8500.00  | -5500.00 |

| U04 | PCI_AD21        | -7500.00  | -5500.00 |

| U05 | PCI_AD22        | -6500.00  | -5500.00 |

| U06 | VSS             | -5500.00  | -5500.00 |

| U07 | VSS             | -4500.00  | -5500.00 |

| U08 | VSS             | -3500.00  | -5500.00 |

| U09 | LCD_DAT_B3      | -2500.00  | -5500.00 |

| U10 | LCD_DAT_G1      | -1500.00  | -5500.00 |

| U11 | LCD_DAT_G7      | -500.00   | -5500.00 |

| U12 | LCD_DAT_R5      | 500.00    | -5500.00 |

| U13 | LCD_EN          | 1500.00   | -5500.00 |

| U14 | SPI1_CS         | 2500.00   | -5500.00 |

| U15 | SPI1_CLK        | 3500.00   | -5500.00 |

| U16 | SPIO_MOSI       | 4500.00   | -5500.00 |

| U17 | UART3_RX        | 5500.00   | -5500.00 |

| U18 | UART2_RX        | 6500.00   | -5500.00 |

| U19 | I2C_SCL        | 7500.00   | -5500.00          |

|-----|----------------|-----------|-------------------|

| U20 | AC97_DATA_0    | 8500.00   | -5500.00          |

| U21 | PWMO           | 9500.00   | -5500.00          |

| U22 | PWM2           | 10500.00  | -5500.00          |

| V01 | PCI_AD26       | -10500.00 | -6500.00          |

| V02 | PCI_AD27       | -9500.00  | -6500.00          |

| V03 | PCI_AD28       | -8500.00  | -6500.00          |

| V04 | PCI_AD25       | -7500.00  | -6500.00          |

| V05 | VGA_A3V3       | -6500.00  | -6500.00          |

| V06 | VGA_A3V3       | -5500.00  | -6500.00          |

| V07 | VGA_A3V3       | -4500.00  | -6500.00          |

| V08 | VGA_HSYNC      | -3500.00  | -6500.00          |

| V09 | LCD_DAT_B4     | -2500.00  | -6500.00          |

| V10 | LCD_DAT_G2     | -1500.00  | -6500.00          |

| V11 | LCD_DAT_R0     | -500.00   | -6500.00          |

| V12 | LCD_DAT_R6     | 500.00    | -6500.00          |

| V13 | GMAC1_TX_CLK_I | 1500.00   | -6500.00          |

| V14 | SPI1_MISO      | 2500.00   | -6500.00          |

| V15 | SPIO_CLK       | 3500.00   | -6500.00          |

| V16 | SPIO_MISO      | 4500.00   | -6500.00          |

| V17 | UART3_TX       | 5500.00   | -6500.00          |

| V18 | UART2_TX       | 6500.00   | -6500.00          |

| V19 | I2C_SDA        | 7500.00   | -6500.00          |

| V20 | AC97_BIT_CLK   | 8500.00   | -6500.00          |

| V21 | PWM1           | 9500.00   | -6500.00          |

| V22 | LPC_AD0        | 10500.00  | -6500.00          |

| WO1 | PCI_AD30       | -10500.00 | -7500.00          |

| W02 | PCI_AD31       | -9500.00  | −7500 <b>.</b> 00 |

| W03 | PCI_GNTN0      | -8500.00  | −7500 <b>.</b> 00 |

| W04 | PCI_AD29       | -7500.00  | −7500 <b>.</b> 00 |

| W05 | PLL_2_AVDD33   | -6500.00  | -7500.00          |

| W06 | VGA_VREFIN     | -5500.00  | -7500.00          |

| W07 | VGA_VSYNC      | -4500.00  | −7500 <b>.</b> 00 |

| W08 | VGA_EN         | -3500.00  | −7500 <b>.</b> 00 |

| W09 | LCD_DAT_B5     | -2500.00  | −7500 <b>.</b> 00 |

| W10 | LCD_DAT_G3     | -1500.00  | −7500 <b>.</b> 00 |

| W11 | LCD_DAT_R1     | -500.00   | -7500.00          |

| W12 | LCD_DAT_R7     | 500.00    | -7500.00          |

| W13 | GMAC1_TX_CLK_O | 1500.00   | −7500 <b>.</b> 00 |

| W14 | SPI1_MOSI      | 2500.00   | -7500.00          |

| W15 | SPIO_CS        | 3500.00   | -7500.00          |

| W16 | UART1_RX       | 4500.00   | −7500 <b>.</b> 00 |

| W17 | UARTO_RX       | 5500.00   | −7500 <b>.</b> 00 |

| W18  | UARTO RTS      | 6500.00   | -7500.00          |

|------|----------------|-----------|-------------------|

| W19  | KB DAT         | 7500.00   | -7500.00          |

| W20  | AC97 DATA I    | 8500.00   | -7500.00          |

| W21  | LPC SERIRQN    | 9500.00   | -7500.00          |

| W22  | LPC AD1        | 10500.00  | -7500.00          |

| Y01  | PCI RESETN     | -10500.00 | -8500.00          |

| Y02  | N/A            | -9500.00  | -8500.00          |

| Y03  | N/A            | -8500.00  | -8500.00          |

| Y04  | PCI_REQN0      | -7500.00  | -8500.00          |

| Y05  | VSS            | -6500.00  | -8500.00          |

| Y06  | VGA_VREFOUT    | -5500.00  | -8500.00          |

| Y07  | VGA_B          | -4500.00  | -8500.00          |

| Y08  | LCD_DAT_B0     | -3500.00  | -8500.00          |

| Y09  | LCD_DAT_B6     | -2500.00  | -8500.00          |

| Y10  | LCD_DAT_G4     | -1500.00  | -8500.00          |

| Y11  | LCD_DAT_R2     | -500.00   | -8500.00          |

| Y12  | LCD_HSYNC      | 500.00    | -8500.00          |

| Y13  | GMAC1_RX_CLK_I | 1500.00   | -8500.00          |

| Y14  | NAND_RD        | 2500.00   | -8500.00          |

| Y15  | NAND_D7        | 3500.00   | -8500.00          |

| Y16  | UART1_TX       | 4500.00   | -8500.00          |

| Y17  | UARTO_DSR      | 5500.00   | -8500.00          |

| Y18  | UARTO_RI       | 6500.00   | -8500.00          |

| Y19  | KB_CLK         | 7500.00   | -8500.00          |

| Y20  | AC97_SYNC      | 8500.00   | -8500.00          |

| Y21  | CAN1_RX        | 9500.00   | -8500.00          |

| Y22  | LPC_AD2        | 10500.00  | -8500.00          |

| AAO1 | N/A            | -10500.00 | -9500.00          |

| AA02 | N/A            | -9500.00  | -9500.00          |

| AAO3 | PCI_GNTN1      | -8500.00  | -9500.00          |

| AA04 | VSS            | -7500.00  | -9500.00          |

| AA05 | PLL_2_AVDD33   | -6500.00  | -9500.00          |

| AA06 | VGA_REXT       | -5500.00  | -9500.00          |

| AA07 | VGA_G          | -4500.00  | -9500.00          |

| AA08 | LCD_DAT_B1     | -3500.00  | -9500.00          |

| AA09 | LCD_DAT_B7     | -2500.00  | -9500.00          |

| AA10 | LCD_DAT_G5     | -1500.00  | -9500.00          |

| AA11 | LCD_DAT_R3     | -500.00   | -9500.00          |

| AA12 | LCD_VSYNC      | 500.00    | -9500.00          |

| AA13 | NAND_ALE       | 1500.00   | -9500.00          |

| AA14 | NAND_CE        | 2500.00   | -9500.00          |

| AA15 | NAND_D6        | 3500.00   | -9500.00          |

| AA16 | UART1_RTS      | 4500.00   | −9500 <b>.</b> 00 |

| AA17 | UARTO TX     | 5500.00   | -9500.00  |

|------|--------------|-----------|-----------|

| AA18 | UARTO_CTS    | 6500.00   | -9500.00  |

| AA19 | MS_DAT       | 7500.00   | -9500.00  |

| AA20 | AC97_RESET   | 8500.00   | -9500.00  |

| AA21 | CAN1_TX      | 9500.00   | -9500.00  |

| AA22 | LPC_AD3      | 10500.00  | -9500.00  |

| AB01 | PCI_REQN1    | -10500.00 | -10500.00 |

| AB02 | PCI_CLK      | -9500.00  | -10500.00 |

| AB03 | PCI_IDSEL    | -8500.00  | -10500.00 |

| AB04 | PLL_2_AVDD33 | -7500.00  | -10500.00 |

| AB05 | VSS          | -6500.00  | -10500.00 |

| AB06 | VGA_COMP     | -5500.00  | -10500.00 |

| AB07 | VGA_R        | -4500.00  | -10500.00 |

| AB08 | LCD_DAT_B2   | -3500.00  | -10500.00 |

| AB09 | LCD_DAT_G0   | -2500.00  | -10500.00 |

| AB10 | LCD_DAT_G6   | -1500.00  | -10500.00 |

| AB11 | LCD_DAT_R4   | -500.00   | -10500.00 |

| AB12 | LCD_CLK      | 500.00    | -10500.00 |

| AB13 | NAND_WR      | 1500.00   | -10500.00 |

| AB14 | NAND_CLE     | 2500.00   | -10500.00 |

| AB15 | NAND_RDY     | 3500.00   | -10500.00 |

| AB16 | UART1_CTS    | 4500.00   | -10500.00 |

| AB17 | UARTO_DTR    | 5500.00   | -10500.00 |

| AB18 | UARTO_DCD    | 6500.00   | -10500.00 |

| AB19 | MS_CLK       | 7500.00   | -10500.00 |

| AB20 | CANO_RX      | 8500.00   | -10500.00 |

| AB21 | CANO_TX      | 9500.00   | -10500.00 |

| AB22 | LPC_FRAMEN   | 10500.00  | -10500.00 |

### 2.2 系统相关引脚定义(8)

表 2-2 系统时钟引脚定义

| No. | 信号名称                | 方向 | 复用 | 上下拉 | 频率    | 描述       | 电压域  |

|-----|---------------------|----|----|-----|-------|----------|------|

| 1   | XTALI               | I  |    |     | 33MHz | 外部晶振时钟输入 | core |

| 2   | XTALO               | 0  |    |     | 33MHz | 外部晶振时钟回送 | core |

| 3   | RTC_CKI             | 1  |    |     | 32KHz | RTC 时钟输入 | RTC  |

| 4   | RTC_CKO             | 0  |    |     | 32KHz | RTC 时钟回送 | RTC  |

| 5   | INTN0               | В  |    |     |       | 中断 0     | core |

| 6   | INTN1               | В  |    |     |       | 中断 1     | core |

| 7   | TEST_CFG            | I  |    |     |       | 测试模块     | core |

| 8   | TEST_BIST_CLK       | I  |    |     | 25MHz | BIST 时钟  | core |

|     | TEST_PHY_CLK        | 1  |    |     | 25MHz | PHY 测试时钟 | core |

|     | TEST_SCAN_M<br>ODEn | ı  |    |     |       | 扫描模式     | core |

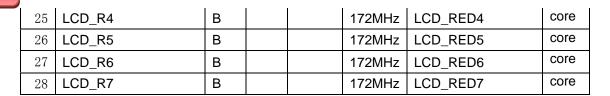

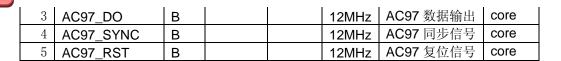

#### 2.3 LCD Controller DVI 接口引脚定义 (28)

表 2-3 LCD Controller DVI 接口引脚定义

| 表 2-3 LCD Controller DVI 接口引脚走又 |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 信号名称                            | 方向                                                                                                                                                                                                                                   | 复用                                                                                                                                                                                                                                                                                                                                                                                                                               | 上下拉                                                                                                                                                                                                                                                                                                                                                                                | 频率     | 描述         | 电压域                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| LCD_CLK                         | В                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    | 172MHz | LCD 时钟     | core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LCD_V                           | В                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    | 172MHz | LCD 列同步    | core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LCD_H                           | В                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    | 172MHz | LCD 行同步    | core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LCD_EN                          | В                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    | 172MHz | LCD 可视使能信号 | core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LCD_B0                          | В                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    | 172MHz | LCD_BLUE0  | core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LCD_B1                          | В                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    | 172MHz | LCD_BLUE1  | core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |